Πίνακας περιεχομένων:

- Συγγραφέας John Day day@howwhatproduce.com.

- Public 2024-01-30 08:32.

- Τελευταία τροποποίηση 2025-01-23 14:39.

Ακολουθήστε περισσότερα από τον συγγραφέα:

Σχετικά με: Mitu Raj - Just a Hobbyst and Learner - Chip Designer - Software Developer - Physics and Mathematics Enthusiast Περισσότερα για το AmCoder »

## Αυτός είναι ο πιο δημοφιλής σύνδεσμος στο Google για εφαρμογή VHDL του ΚΟΡΔΙΚΟΥ ΑΛΓΟΡΙΘΜΟΥ για τη δημιουργία κύματος ημιτόνου και συνημιτόνου τα πολλα χρονια Ο CORDIC είναι ένας τέτοιος αλγόριθμος που δεν είναι παρά ένα σύνολο αλλαγών και προσθήκης λογικών που χρησιμοποιούνται για τον υπολογισμό ενός ευρέος φάσματος συναρτήσεων, συμπεριλαμβανομένων ορισμένων τριγωνομετρικών, υπερβολικών, γραμμικών και λογαριθμικών συναρτήσεων. Αυτός είναι ο αλγόριθμος που χρησιμοποιείται σε αριθμομηχανές κλπ. Έτσι, χρησιμοποιώντας απλούς μετατοπιστές και αθροιστές μπορούμε να σχεδιάσουμε ένα υλικό με λιγότερη πολυπλοκότητα αλλά ισχύ DSP χρησιμοποιώντας κορδικό αλγόριθμο. Ως εκ τούτου, μπορεί να σχεδιαστεί ως γυμνό σχέδιο RTL σε VHDL ή Verilog χωρίς χρήση αποκλειστικών μονάδων κυμαινόμενου σημείου ή πολύπλοκων μαθηματικών IP.

Βήμα 1: VHDL και Modelsim

Εδώ ο κορδικός αλγόριθμος υλοποιείται χρησιμοποιώντας VHDL για να δημιουργήσει ημιτονοειδές κύμα και κυματοειδές κύμα. Μπορεί να εξάγει ημιτόνο και συνημίτονο γωνίας εισόδου με μεγάλη ακρίβεια. Ο κωδικός είναι συνθετός στο FPGA. Το Modelsim χρησιμοποιείται για την προσομοίωση του σχεδιασμού και του πάγκου δοκιμών.

Βήμα 2: Κώδικας VHDL για το σχέδιο και τον πάγκο δοκιμών

Η δυαδική τεχνική κλιμάκωσης χρησιμοποιείται για την αναπαράσταση αριθμών κυμαινόμενων σημείων.

Παρακαλώ περάστε από τα συνημμένα έγγραφα πριν κωδικοποιήσετε.

Πηγαίνετε μέσω προσομοίωσης cordic_v4.vhd - Ο σχεδιασμός - Η είσοδος είναι γωνία σε 32 bits + bit υπογραφής. μπορεί να επεξεργαστεί οποιαδήποτε γωνία από 0 έως +/- 360 μοίρες με ακρίβεια εισόδου 0.000000000233 μοίρα. Κατά την εισαγωγή εισόδου -> MSB είναι το bit του σημείου και τα υπόλοιπα 32 bits αντιπροσωπεύουν το μέγεθος. με ακρίβεια 0,00001526. Λάβετε υπόψη ότι η έξοδος εμφανίζεται σε μορφή φιλοφρόνησης 2 εάν η αντίστοιχη τιμή ημιτόνου ή cos είναι αρνητική. Προσομοίωση testb.vhd - Test Bench For The Design (1) Γωνίες εισαγωγής και επαναφορά έλξης = '0'. Μετά από δύο βήματα προσομοίωσης, τραβήξτε επαναφορά στο "1" και "εκτελέστε όλα". (2) Στο παράθυρο προσομοίωσης ορίστε τη ρίζα των σημάτων sin και cos ως δεκαδικά και μορφή> Αναλογικό (αυτόματο). (3) Σμίκρυνση για να δείτε την κυματομορφή σωστά.

Βήμα 3: Επισυνάπτονται αρχεία

(1) cordic_v4.vhd - Σχεδιασμός. (2) testb.vhd - Δοκιμαστικός πάγκος για το σχέδιο.

(3) Έγγραφο σχετικά με τον τρόπο εξαναγκασμού εισόδων γωνίας και μετατροπής των δυαδικών αποτελεσμάτων.

Ενημέρωση: ΑΥΤΑ ΤΑ ΑΡΧΕΙΑ ΕΙΝΑΙ ΛΟΓΑΡΙΑ ΚΑΙ ΔΕΝ ΠΑΡΕΧΟΝΤΑΙ ΑΛΛΑ. ΠΑΡΑΚΑΛΟΥΜΕ ΧΡΗΣΗ ΑΡΧΕΙΩΝ ΑΠΟ ΕΠΟΜΕΝΟ ΒΗΜΑ

Βήμα 4: Mini -Cordic IP Core - 16 Bit

Ο περιορισμός της παραπάνω εφαρμογής είναι αργή, χαμηλότερη συχνότητα λειτουργίας ρολογιού λόγω υπολογισμών σε έναν κύκλο ρολογιού. Mini-Cordic IP Core- 16 Bit

- Κρίσιμες διαδρομές που διανέμονται σε πολλούς κύκλους για τη βελτίωση της απόδοσης.- Γρηγορότερα- Ο δοκιμασμένος σχεδιασμός FPGA συνέθεσε έως και ρολόι 100 Mhz.- Βελτιστοποιήθηκε περισσότερη περιοχή σε HDL, μικρότερο υλικό.- Προστέθηκαν σήματα φόρτωσης και ολοκλήρωσης.- Μόνο το μειονέκτημα είναι μικρότερη ανάλυση σε σύγκριση με το προηγούμενο. Testbench:

πλήρως αυτοματοποιημένη από 0 έως 360 μοιρών γωνιακές εισόδους

Επισυνάπτονται αρχεία: 1) μίνι κορδικό κύριο αρχείο vhdl2) μίνι κορδικός πάγκος δοκιμών 3) Εγχειρίδιο μίνι Cordic IP 4) 4) Έγγραφο σχετικά με τον τρόπο εξαναγκασμού γωνιών και μετατροπής αποτελεσμάτων

Για οποιαδήποτε απορία, μη διστάσετε να επικοινωνήσετε μαζί μου:

Μίτου Ρατζ

ακολουθήστε με:

ταχυδρομείο: iammituraj@gmail.com

### Συνολικές λήψεις: 325 έως 01-05-2021 ###

### Τελευταία επεξεργασία κώδικα: Ιούλιος-07-2020 ###

Συνιστάται:

Self Balancing Robot - Αλγόριθμος ελέγχου PID: 3 βήματα

Self Balancing Robot - Αλγόριθμος Ελέγχου PID: Αυτό το έργο σχεδιάστηκε επειδή με ενδιέφερε να μάθω περισσότερα για τους Αλγόριθμους Ελέγχου και πώς να εφαρμόσω αποτελεσματικά λειτουργικούς βρόχους PID. Το έργο βρίσκεται ακόμη σε φάση ανάπτυξης καθώς δεν έχει ακόμη προστεθεί μια μονάδα Bluetooth η οποία θα

Επιτραπέζιο παιχνίδι Τεχνητή Νοημοσύνη: ο αλγόριθμος Minimax: 8 βήματα

Επιτραπέζιο παιχνίδι Τεχνητή Νοημοσύνη: ο αλγόριθμος Minimax: Αναρωτηθήκατε ποτέ πώς κατασκευάζονται οι υπολογιστές με τους οποίους παίζετε στο σκάκι ή στα πούλια; Λοιπόν, μην κοιτάξετε πέρα από αυτό το Instructable γιατί θα σας δείξει πώς να φτιάξετε μια απλή αλλά αποτελεσματική τεχνητή νοημοσύνη (AI) χρησιμοποιώντας τον αλγόριθμο Minimax! Χρησιμοποιώντας τη

Βασικό χρονόμετρο χρησιμοποιώντας VHDL και Basys3 Board: 9 βήματα

Βασικό Χρονόμετρο Χρήση VHDL και Basys3 Board: Καλώς ορίσατε στο διδακτικό πώς να φτιάξετε ένα χρονόμετρο χρησιμοποιώντας τον βασικό πίνακα VHDL και Basys 3. Είμαστε ενθουσιασμένοι που θα μοιραστούμε το έργο μας μαζί σας! Αυτό ήταν ένα τελικό έργο για το μάθημα CPE 133 (Digital Design) στο Cal Poly, SLO το Φθινόπωρο του 2016. Το έργο που χτίζουμε

Tic Tac Toe στο Arduino με AI (αλγόριθμος Minimax): 3 βήματα

Tic Tac Toe στο Arduino With AI (Minimax Algorithm): Σε αυτό το Instructable θα σας δείξω πώς να φτιάξετε ένα παιχνίδι Tic Tac Toe με AI χρησιμοποιώντας Arduino. Μπορείτε είτε να παίξετε ενάντια στο Arduino είτε να παρακολουθήσετε το Arduino να παίζει εναντίον του. Χρησιμοποιώ έναν αλγόριθμο που ονομάζεται " minimax algorithm "

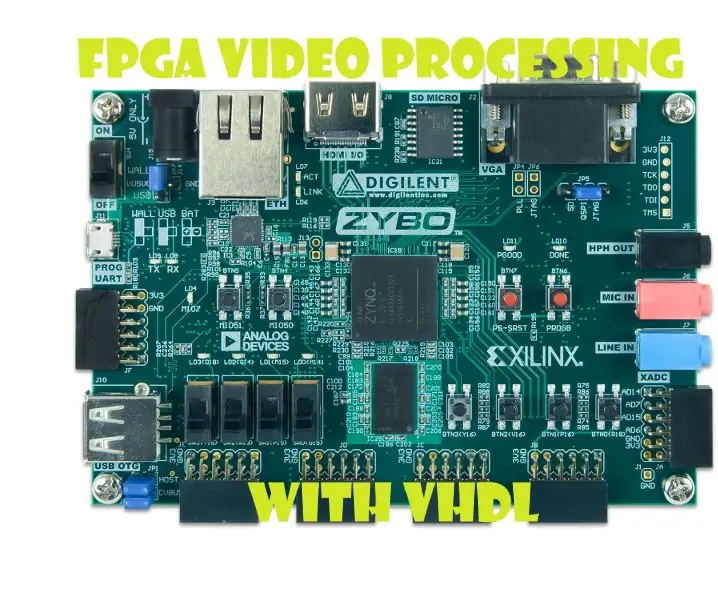

Επεξεργασία βίντεο χρησιμοποιώντας VHDL και ένα Zybo: 10 βήματα

Επεξεργασία βίντεο χρησιμοποιώντας VHDL και Zybo: Τα FPGA είναι ταχύτερα από τα CPU για επεξεργασία, επειδή μπορούν να κάνουν πολλούς υπολογισμούς παράλληλα Σημείωση: Αυτό το έργο είναι ακόμη υπό κατασκευή και πρόκειται να βελτιωθεί (μόλις έχω χρόνο). Εν τω μεταξύ ταξιδεύω στον κόσμο