Πίνακας περιεχομένων:

- Βήμα 1: Τι είναι το Vivado HLS;

- Βήμα 2: Βιβλιοθήκη βίντεο HLS

- Βήμα 3: Σύνθεση

- Βήμα 4: Έκδοση και άλλες πληροφορίες για εξαγωγή

- Βήμα 5: Εξαγωγή σε βιβλιοθήκη IP Vivado

- Βήμα 6: Ανάλυση σύνθεσης και εξαγωγής

- Βήμα 7: Προσθήκη της Βιβλιοθήκης IP στο Vivado

- Βήμα 8: Κάντε αναβάθμιση

- Βήμα 9: Πρόσθετες λεπτομέρειες και πληροφορίες

- Βήμα 10: Έξοδος και είσοδος

- Βήμα 11: Εγγραφή διασύνδεσης AXI Register

- Βήμα 12: Dataflow Pragma

- Συγγραφέας John Day day@howwhatproduce.com.

- Public 2024-01-30 08:38.

- Τελευταία τροποποίηση 2025-01-23 14:39.

Θέλατε ποτέ να κάνετε επεξεργασία σε πραγματικό χρόνο σε βίντεο χωρίς να προσθέσετε μεγάλη καθυστέρηση ή σε ενσωματωμένο σύστημα; Μερικές φορές χρησιμοποιούνται FPGAs (Field Programmable Gate Arrays). Ωστόσο, η συγγραφή αλγορίθμων επεξεργασίας βίντεο σε γλώσσες προδιαγραφών υλικού όπως το VHDL ή το Verilog είναι στην καλύτερη περίπτωση απογοητευτική. Εισαγάγετε το Vivado HLS, το εργαλείο Xilinx που σας επιτρέπει να προγραμματίζετε σε περιβάλλον C ++ και να δημιουργείτε κώδικα γλώσσας προδιαγραφών υλικού από αυτό.

Απαιτούμενα λογισμικά:

- Vivado HLS

- Vivado

- (Εάν χρησιμοποιείτε τους καταχωρητές AXI) Vivado SDK

(Προαιρετικό) Κατεβάστε τα παραδείγματα του Xilinx εδώ:

Παραδείγματα βίντεο Xilinx HLS

Βήμα 1: Τι είναι το Vivado HLS;

Το Vivado HLS είναι ένα εργαλείο που χρησιμοποιείται για τη μετατροπή κώδικα τύπου c ++ σε δομές υλικού που μπορούν να εφαρμοστούν σε FPGA. Περιλαμβάνει IDE για την πραγματοποίηση αυτής της ανάπτυξης. Μόλις ολοκληρώσετε την ανάπτυξη του κώδικα για το HLS, μπορείτε να εξάγετε τη δημιουργημένη IP σας σε μορφή για χρήση με το Vivado.

Κατεβάστε τα συνημμένα αρχεία και τοποθετήστε τα κοντά στο σημείο που θα δημιουργήσετε το έργο σας. (μετονομάστε τα ξανά σε "top.cpp" και "top.h" εάν έχουν τυχαίο όνομα)

Βήμα 2: Βιβλιοθήκη βίντεο HLS

Η Βιβλιοθήκη βίντεο HLS έχει τεκμηρίωση με σχέδια αναφοράς σε αυτό το έγγραφο: XAPP1167Ένας άλλος καλός πόρος είναι η σελίδα Xilinx Wiki σχετικά με αυτό.

Ξεκινήστε το Vivado HLS.

Δημιουργήστε ένα νέο έργο.

Πάρτε τα αρχεία που κατεβάσατε στο προηγούμενο βήμα και προσθέστε τα ως αρχεία προέλευσης. (Σημείωση: τα αρχεία δεν αντιγράφονται στο έργο, αλλά αντίθετα παραμένουν εκεί που είναι)

Στη συνέχεια, χρησιμοποιήστε το κουμπί Αναζήτηση για να επιλέξετε την κορυφαία λειτουργία.

Στην επόμενη σελίδα, επιλέξτε το τμήμα Xilinx που χρησιμοποιείτε.

Βήμα 3: Σύνθεση

Λύση => Εκτέλεση C Synthesis => Ενεργή λύση

Μετά από 7 227.218 δευτερόλεπτα, θα πρέπει να γίνει. (Σημείωση: ο πραγματικός χρόνος σύνθεσής σας θα διαφέρει ανάλογα με πολλούς παράγοντες)

Βήμα 4: Έκδοση και άλλες πληροφορίες για εξαγωγή

Οι αριθμοί έκδοσης αλληλεπιδρούν με το Vivado για να έχετε τη δυνατότητα να ενημερώσετε την IP σε ένα σχέδιο. Εάν πρόκειται για αλλαγή δευτερεύουσας έκδοσης, μπορεί να γίνει στη θέση της, ενώ οι μεγάλες αλλαγές της έκδοσης απαιτούν να προσθέσετε μη αυτόματα το νέο μπλοκ και να αφαιρέσετε το παλιό. Εάν οι διεπαφές σας δεν έχουν αλλάξει και η ενημέρωση έκδοσης είναι ήσσονος σημασίας, η ενημέρωση μπορεί να είναι γίνεται εντελώς αυτόματα πατώντας το κουμπί ενημέρωσης IP. Μπορείτε να εκτελέσετε το "report_ip_status" στην κονσόλα Vivado tcl για να δείτε την κατάσταση της IP σας.

Ορίστε τους αριθμούς έκδοσης και άλλες πληροφορίες στο Solution => Solution Settings…

Εναλλακτικά, αυτές οι ρυθμίσεις μπορούν να οριστούν κατά την εξαγωγή.

Βήμα 5: Εξαγωγή σε βιβλιοθήκη IP Vivado

Λύση => Εξαγωγή RTL

Εάν δεν ορίσατε τις λεπτομέρειες της βιβλιοθήκης IP στο προηγούμενο βήμα, μπορείτε να το κάνετε τώρα.

Βήμα 6: Ανάλυση σύνθεσης και εξαγωγής

Σε αυτήν την οθόνη μπορούμε να δούμε τα στατιστικά στοιχεία σχετικά με την εξαγόμενη μονάδα μας, δείχνοντας ότι ανταποκρίνεται στην περίοδο ρολογιού μας των 10ns (100MHz) και πόσο από κάθε πόρο που χρησιμοποιεί.

Με έναν συνδυασμό αυτού, της σύνθετης έκθεσής μας και της ανάλυσης ροής δεδομένων, μπορούμε να δούμε ότι χρειάζονται 317338 κύκλοι ρολογιού * περίοδος ρολογιού 10ns * 14 στάδια αγωγών = 0,04442732 δευτερόλεπτα. Αυτό σημαίνει ότι η συνολική καθυστέρηση που προστίθεται από την επεξεργασία της εικόνας μας είναι μικρότερη από το ένα εικοστό του δευτερολέπτου (όταν χρονομετρηθεί στα στοχευμένα 100MHz).

Βήμα 7: Προσθήκη της Βιβλιοθήκης IP στο Vivado

Για να χρησιμοποιήσετε το συνθετικό μπλοκ IP σας, θα χρειαστεί να το προσθέσετε στο Vivado.

Στο Vivado προσθέστε ένα αποθετήριο IP στο έργο σας πηγαίνοντας στον κατάλογο IP και κάντε δεξί κλικ επιλέγοντας "Προσθήκη αποθήκης …"

Μεταβείτε στον κατάλογο έργου Vivado HLS και επιλέξτε τον κατάλογο λύσεων.

Θα πρέπει να αναφέρει την IP που βρήκε.

Βήμα 8: Κάντε αναβάθμιση

Μερικές φορές χρειάζεται να κάνετε αλλαγές στο μπλοκ HLS αφού το συμπεριλάβετε σε σχέδιο Vivado.

Για να το κάνετε αυτό, μπορείτε να κάνετε τις αλλαγές και να επανασυνθέσετε και να εξάγετε την IP με έναν υψηλότερο αριθμό έκδοσης (δείτε λεπτομέρειες στο προηγούμενο βήμα σχετικά με τις μεγάλες αλλαγές στον αριθμό του αριθμού έκδοσης).

Αφού αλλάξετε την εξαγωγή της νέας έκδοσης, ανανεώστε τα αποθετήρια IP σας στο Vivado. Αυτό μπορεί είτε να γίνει όταν η Vivado παρατηρήσει ότι η IP έχει αλλάξει στο χώρο αποθήκευσης, είτε ενεργοποιείται χειροκίνητα. (Σημείωση, εάν ανανεώσετε τα αποθετήρια IP σας μετά την έναρξη, αλλά πριν ολοκληρωθεί η εξαγωγή σε HLS, η IP δεν θα είναι προσωρινά εκεί, περιμένετε να τελειώσει και να ανανεωθεί ξανά.)

Σε αυτό το σημείο θα πρέπει να εμφανιστεί ένα παράθυρο με τις πληροφορίες ότι έχει αλλάξει μια διεύθυνση IP στο δίσκο και σας δίνει την επιλογή να την ενημερώσετε με ένα κουμπί "Upgrade Selected". Εάν η αλλαγή ήταν μια μικρή έκδοση και καμία από τις διεπαφές δεν άλλαξε, στη συνέχεια, πατώντας αυτό το κουμπί θα αντικαταστήσει αυτόματα την παλιά IP με τη νέα, διαφορετικά μπορεί να απαιτηθεί περισσότερη εργασία.

Βήμα 9: Πρόσθετες λεπτομέρειες και πληροφορίες

Τα παρακάτω βήματα παρέχουν περισσότερες πληροφορίες σχετικά με τον τρόπο λειτουργίας της σύνθεσης HLS και τι μπορείτε να κάνετε με αυτήν.

Για ένα παράδειγμα έργου που χρησιμοποιεί ένα μπλοκ IP συνθεμένης HLS, δείτε αυτό το διδακτικό.

Βήμα 10: Έξοδος και είσοδος

Οι έξοδοι και οι είσοδοι στο τελικό μπλοκ IP καθορίζονται από μια ανάλυση που κάνει ο συνθέτης της ροής δεδομένων μέσα και έξω από την κορυφαία συνάρτηση.

Παρόμοια με το VHDL ή το verilog, το HLS σάς επιτρέπει να καθορίσετε λεπτομέρειες σχετικά με τις συνδέσεις μεταξύ IP. Αυτές οι γραμμές είναι παραδείγματα αυτού:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE θύρα άξονα = video_in bundle = INPUT_STREAM #pragma HLS INTERFACE port port = video_out bundle = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BLUSFL

Μπορείτε να δείτε πώς οι θύρες που εμφανίζονται στο μπλοκ IP επηρεάζονται από αυτές τις οδηγίες.

Βήμα 11: Εγγραφή διασύνδεσης AXI Register

Για να έχετε είσοδο/έξοδο από/από το μπλοκ IP σας στο PS, ένας καλός τρόπος για να το κάνετε αυτό είναι μέσω μιας διεπαφής AXI.

Μπορείτε να το καθορίσετε στον κωδικό HLS, συμπεριλαμβανομένων των αντισταθμίσεων που θα χρησιμοποιηθούν για να αποκτήσετε πρόσβαση στην τιμή αργότερα ως εξής:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BUS offset = 0x14

#pragma HLS INTERFACE s_axilite port = y bundle = CONTROL_BUS offset = 0x1C #pragma HLS dataflow

x = 42;

y = 0xDEADBEEF; }

Αφού συνδεθείτε σωστά στο Vivado, μπορείτε να αποκτήσετε πρόσβαση στις τιμές χρησιμοποιώντας αυτόν τον κωδικό στο Vivado SDK:

#include "paramet.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Αυτό θα σας κάνει να καταλήξετε με 42 σε x και 0xdeadbeef σε y

Βήμα 12: Dataflow Pragma

Μέσα στο #pragma DATAFLOW ο τρόπος εφαρμογής του κώδικα αλλάζει από το κανονικό C ++. Ο κώδικας διοχετεύεται έτσι ώστε όλες οι οδηγίες να εκτελούνται ανά πάσα στιγμή σε διαφορετικά μέρη των δεδομένων (Σκεφτείτε το σαν μια γραμμή συναρμολόγησης σε ένα εργοστάσιο, κάθε σταθμός λειτουργεί συνεχώς κάνοντας μια λειτουργία και μεταφέροντάς την στον επόμενο σταθμό)

από την εικόνα μπορείτε να δείτε ότι κάθε μία από τις οδηγίες

Παρά το γεγονός ότι φαίνονται φυσιολογικές μεταβλητές, τα αντικείμενα img εφαρμόζονται στην πραγματικότητα ως μικρά buffer μεταξύ των εντολών. Η χρήση μιας εικόνας ως είσοδο σε μια συνάρτηση την "καταναλώνει" και την καθιστά πλέον άχρηστη. (Εξ ου και η ανάγκη για διπλές εντολές)

Συνιστάται:

The Ultimate Knife Block: 11 βήματα (με εικόνες)

The Ultimate Knife Block: Όλοι έχουμε πάει εκεί, κόβοντας λαχανικά με ένα μαχαίρι τόσο αμβλύ που θα ήταν πιο αποτελεσματικό να χρησιμοποιήσετε ένα κουταλάκι του γλυκού. Εκείνη τη στιγμή, αναλογίζεστε πώς φτάσατε εκεί: τα μαχαίρια σας ήταν κοφτερά σαν ξυράφια όταν τα αγοράσατε, αλλά τώρα, τρία χρόνια μετά

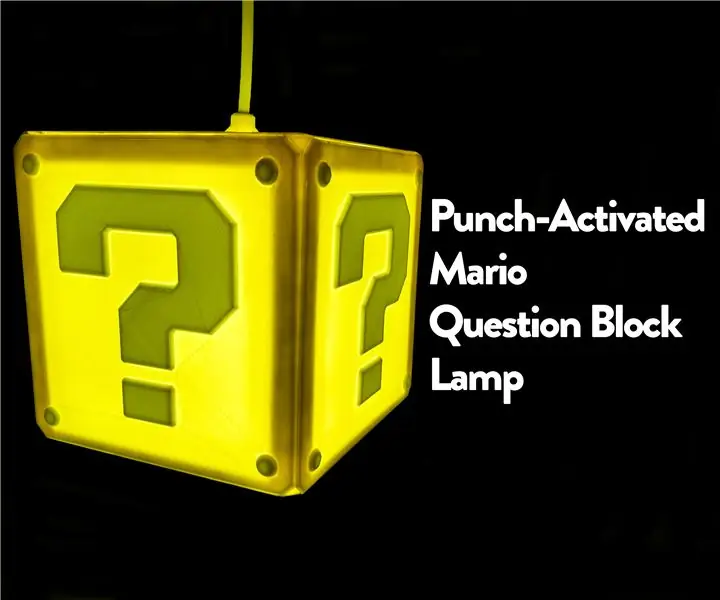

Punch Activated Mario Question Block Lamp: 8 βήματα (με εικόνες)

Punch Activated Mario Question Block Lamp: Τα παιχνίδια Super Mario ήταν τα παιδικά μου χρόνια. Πάντα ήθελα να έχω μερικά από τα στηρίγματα στα παιχνίδια και τώρα που έχω τα εργαλεία για να το κάνω, αποφάσισα να ξεκινήσω να τα φτιάχνω. Το πρώτο από αυτά στη λίστα μου είναι το Question Block. Κατάφερα να φτιάξω το

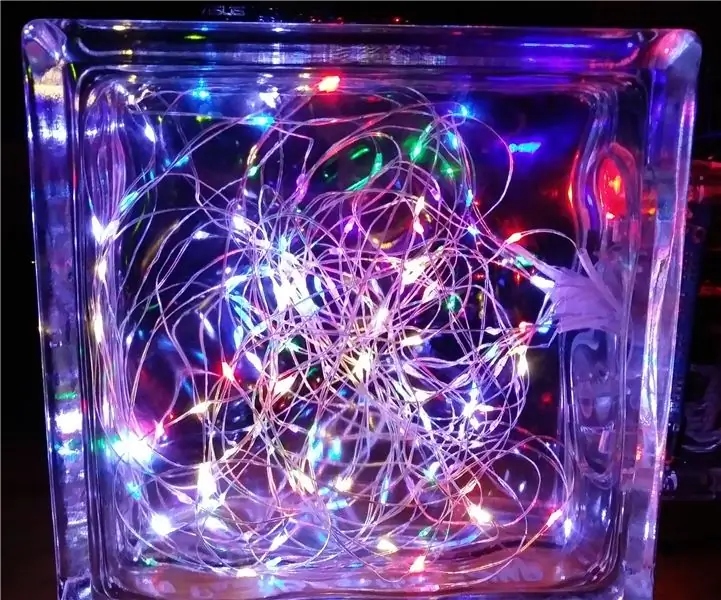

Breathe: Fading Fairy Fairy in a Glass Block: 6 βήματα

Breathe: Fading Fairy Fairy in a Glass Block: Για τα Χριστούγεννα φέτος αποφάσισα να χρησιμοποιήσω ένα γυάλινο μπλοκ, ένα χειριστήριο PWM και μερικά κορδόνια φωτός νεράιδας LED για να κάνω στη γυναίκα μου ένα πολύχρωμο δώρο

Πώς να χρησιμοποιήσετε το Vivado Simluation: 6 βήματα

Πώς να χρησιμοποιήσετε το Vivado Simluation: Έχω κάνει αυτό το έργο προσομοίωσης για ένα online μάθημα. Το έργο είναι γραμμένο από τη Verilog. Θα χρησιμοποιήσουμε την προσομοίωση στο Vivado για να απεικονίσουμε την κυματομορφή στο enable_sr (ενεργοποίηση ψηφίου) από το έργο παρακολούθησης διακοπών που δημιουργήθηκε προηγουμένως. Επιπλέον, θα μας

Camara De Video En Carro De Radio Control / Video Camera on R / C Truck: 5 βήματα

Camara De Video En Carro De Radio Control / Video Camera on R / C Truck: Este Instruccionable presentado en Espanol e Ingles. Αυτά τα Εκπαιδευτικά παρουσιάζονται στα Ισπανικά και Αγγλικά