Πίνακας περιεχομένων:

- Βήμα 1: Δημιουργία μονάδας PWM- Αρχείο προέλευσης

- Βήμα 2: Δημιουργία μονάδας PWM- Ρύθμιση Vivado

- Βήμα 3: Δημιουργία μονάδας PWM- Δημιουργία αρχείου έργου

- Βήμα 4: Δημιουργία μονάδας PWM- Σχεδιασμός μπλοκ και ρύθμιση αρχείων περιορισμού (I)

- Βήμα 5: Δημιουργία μονάδας PWM- Σχεδιασμός μπλοκ και ρύθμιση αρχείων περιορισμών (II)

- Βήμα 6: Δημιουργία μονάδας PWM- Σχεδιασμός μπλοκ και ρύθμιση αρχείων περιορισμού (III)

- Βήμα 7: Δημιουργία μονάδας PWM- Σχεδιασμός μπλοκ και ρύθμιση αρχείων περιορισμού (IV)

- Βήμα 8: Δημιουργία μονάδας PWM- Σχεδιασμός μπλοκ και ρύθμιση αρχείων περιορισμού (V)

- Βήμα 9: Δημιουργία μονάδας PWM- Εγκατάσταση υλικού

- Βήμα 10: Δημιουργία μονάδας PWM- Δημιουργήστε Bitstream και ξεκινήστε το SDK

- Βήμα 11: Δημιουργία μονάδας PWM- Δημιουργήστε μια νέα εφαρμογή στο Xilinx SDK

- Βήμα 12: Δημιουργία μονάδας PWM- Επισκόπηση του Project Explorer (I)

- Βήμα 13: Δημιουργία μονάδας PWM- Επισκόπηση του Project Explorer (II)

- Βήμα 14: Δημιουργία μονάδας PWM- Επισκόπηση του Project Explorer (III)

- Βήμα 15: Δημιουργία μονάδας PWM- Λήψη λειτουργίας PWM (I)

- Βήμα 16: Δημιουργία μονάδας PWM- Λήψη λειτουργίας PWM (II)

- Βήμα 17: Δημιουργία μονάδας PWM- Λύση λειτουργίας PWM (III)

- Βήμα 18: Δημιουργία μονάδας PWM- Κάντε το να τρέξει

- Βήμα 19: Επεξεργασία ροής βίντεο σε Digilent ZYBO με OV7670

- Βήμα 20: Πλήρες διάγραμμα μπλοκ

- Βήμα 21: Συνδέστε το OV7670 στο ZYBO

- Βήμα 22: Δημιουργία Σχεδιασμού Μπλοκ

- Βήμα 23: Προσθέστε αρχεία VHDL για έλεγχο και λήψη φωτογραφικής μηχανής OV7670

- Βήμα 24: Προσθήκη αρχείου περιορισμών

- Βήμα 25: Προσθέστε IP Repo για HLS IP

- Βήμα 26: Προσθέστε ενότητες και IP

- Βήμα 27: Ρυθμίσεις διαμόρφωσης IP

- Βήμα 28: Προσθήκη και ρύθμιση παραμέτρων του IP IP Block

- Βήμα 29: Μέρος 1. Δημιουργία μονάδας PWM για Servo Motors

- Βήμα 30: Πλευρικές συνδέσεις εισόδου βίντεο (επισημαίνεται aclk)

- Βήμα 31: Συνδέσεις στο OV7670

- Βήμα 32: Συνδέσεις στο Video Out Side

- Βήμα 33: Εκτελέστε Block and Connection Automation

- Βήμα 34: Δημιουργήστε περιτύλιγμα HDL

- Βήμα 35: Δημιουργία Bitstream, Εξαγωγή υλικού σε SDK, Εκκίνηση SDK από το Vivado

- Βήμα 36: SDK (χωρίς FreeRTOS)

- Βήμα 37: Εφαρμογή FreeRTOS

- Βήμα 38: Οδηγίες χρήσης

- Βήμα 39: Αναφορές και σύνδεσμοι

- Συγγραφέας John Day day@howwhatproduce.com.

- Public 2024-01-30 08:38.

- Τελευταία τροποποίηση 2025-01-23 14:39.

Ξεκινήστε στο πρώτο βήμα για λεπτομέρειες σχετικά με τη δημιουργία ενός σερβοελεγκτή PWM 2 αξόνων.

Ξεκινήστε από το τεράστιο μπλοκ διάγραμμα (Βήμα 19) για το πλήρες έργο.

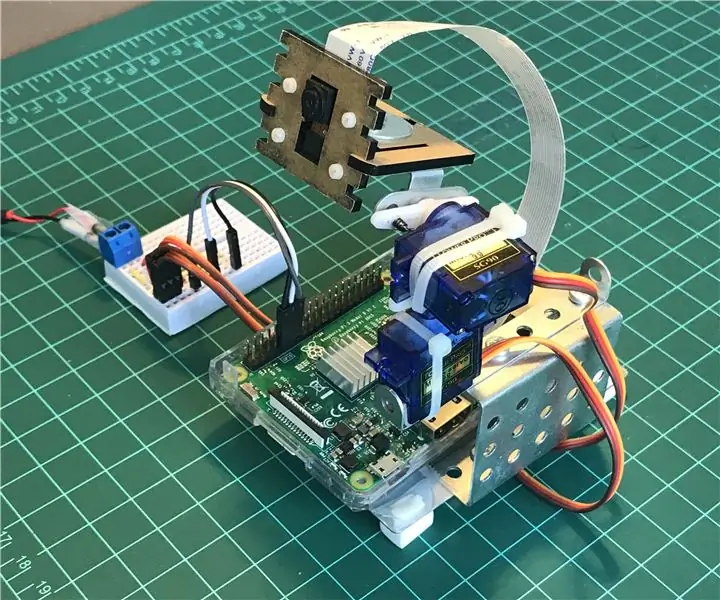

Κάμερα + Ρύθμιση Pan/Tilt που χρησιμοποιήσαμε:

Το PmodCON3 από το Digilent χρησιμοποιήθηκε για τη σύνδεση των servos.

Βήμα 1: Δημιουργία μονάδας PWM- Αρχείο προέλευσης

Βήμα 2: Δημιουργία μονάδας PWM- Ρύθμιση Vivado

Πρώτα, κατεβάστε τον ιστότοπο Vivado Design Suite From Xilinx. Εγκαταστήστε όλη τη σουίτα σχεδιασμού, συμπεριλαμβανομένου του κιτ ανάπτυξης λογισμικού Vivado (SDK). Αυτό το έργο χρησιμοποιεί την έκδοση 2017.2.

Εν τω μεταξύ, το Digilent Adept 2 θα πρέπει επίσης να εγκατασταθεί ως πρόγραμμα οδήγησης πλακέτας Zybo.

Βήμα 3: Δημιουργία μονάδας PWM- Δημιουργία αρχείου έργου

Πριν δημιουργήσετε ένα αρχείο έργου, θα πρέπει να βεβαιωθείτε ότι έχετε ήδη εγκαταστήσει σωστά το αρχείο Zybo ως οδηγό εδώ:

Vivado Version 2015.1 και μεταγενέστερη εγκατάσταση αρχείου πίνακα

Άνοιγμα Vivado 2017.2. Στο Quick Start, κάντε κλικ στο Δημιουργία έργου -> Επόμενο -> Όνομα έργου (Ονομάστε το όνομα του έργου σας εδώ) -> Τύπος έργου. Στον Τύπο έργου, επιλέξτε RTL Project και σημειώστε στο "Μην καθορίσετε πηγές αυτήν τη στιγμή". Στη συνέχεια, για το Προεπιλεγμένο μέρος, επιλέξτε "Πίνακες" και "Zybo" ως Εμφανιζόμενο Όνομα. Στη συνέχεια, κάντε κλικ στο κουμπί Τέλος για να ξεκινήσει το έργο.

Βήμα 4: Δημιουργία μονάδας PWM- Σχεδιασμός μπλοκ και ρύθμιση αρχείων περιορισμού (I)

Στο Flow Navigator, κάντε κλικ στο "" Create Block Design "και, στη συνέχεια, πατήστε OK. κάντε κλικ στο σύμβολο "+" για να προσθέσετε τα απαραίτητα IP. Προσθήκη:

- Ένα σύστημα επεξεργασίας ZYNQ7 Δύο χρονοδιακόπτες AXI

- Δύο χρονοδιακόπτες AXI

Βήμα 5: Δημιουργία μονάδας PWM- Σχεδιασμός μπλοκ και ρύθμιση αρχείων περιορισμών (II)

Μετά την προσθήκη IP, εκτελέστε την αυτοματοποίηση αποκλεισμού και την αυτοματοποίηση σύνδεσης. Μόλις ολοκληρωθεί η αυτοματοποίηση, στο μπλοκ "axi_timer_0", κάντε δεξί κλικ στο pwm0 -> Make External. Ονομάστε την εξωτερική καρφίτσα pwm0 ως pwm_Xaxis. Επίσης, επαναλάβετε την παραπάνω διαδικασία στο μπλοκ "axi_timer_1" και ονομάστε την εξωτερική καρφίτσα pwm0 ως pwm_Zaxis.

Βήμα 6: Δημιουργία μονάδας PWM- Σχεδιασμός μπλοκ και ρύθμιση αρχείων περιορισμού (III)

Παρατηρήστε ότι κάθε φορά που τελειώνουμε το Block Design στο Vivado, πρέπει να δημιουργήσουμε ένα HDL Wrapper. Δεδομένου ότι θα είναι η ενότητα ανώτατου επιπέδου για κάθε έργο.

Βήμα 7: Δημιουργία μονάδας PWM- Σχεδιασμός μπλοκ και ρύθμιση αρχείων περιορισμού (IV)

Τώρα, πρέπει να ρυθμίσουμε το αρχείο περιορισμού μας για να εκχωρήσουμε ακίδες συνδεδεμένες στο μπλοκ διάγραμμά μας. Κλείστε το παράθυρο Block Design, Στην καρτέλα Πηγές, "Προσθήκη πηγών"-> Προσθήκη ή δημιουργία περιορισμών-> προσθέστε το Zybo-Master.xdc ως αρχεία περιορισμών.

Βήμα 8: Δημιουργία μονάδας PWM- Σχεδιασμός μπλοκ και ρύθμιση αρχείων περιορισμού (V)

Ανοίξτε το αρχείο περιορισμού Zybo-Master.xdc από το φάκελο Περιορισμοί, αποσυνδέστε τις θύρες που θέλουμε να ορίσουμε ως σήματα εξόδου και μετονομάστε "get_ports {XXXX}", το οποίο XXXX υποδηλώνει την εξωτερική ακίδα που ονομάζεται στο διάγραμμα αποκλεισμού. Η ρύθμιση του αρχείου περιορισμού εμφανίζεται στο σχήμα.

Βήμα 9: Δημιουργία μονάδας PWM- Εγκατάσταση υλικού

Συνδέστε τους σερβοκινητήρες στο Pmod CON3. Το TowerPro SG90 είναι το μοντέλο σερβοκινητήρα που χρησιμοποιήσαμε σε αυτό το έργο. Για τα καλώδια σερβοκινητήρα, το πορτοκαλί σύρμα αντιπροσωπεύει το σήμα PWM, συνδεδεμένο με τον πείρο SIG στο Pmod CON3. Το κόκκινο καλώδιο Vcc είναι ένα καλώδιο τροφοδοσίας συνδεδεμένο με τον πείρο VS στο Pmod CON3. Τέλος, το καφέ σύρμα Gnd είναι ένα καλώδιο γείωσης που συνδέεται με τον πείρο GND. Στη συνέχεια, εισαγάγετε το Pmod CON3 στην επάνω σειρά της θύρας JD στον πίνακα Zybo.

Βήμα 10: Δημιουργία μονάδας PWM- Δημιουργήστε Bitstream και ξεκινήστε το SDK

1. Στην καρτέλα Project Navigator, εκτελέστε Generate BitStream.

2. Εξαγωγή υλικού: Αρχείο> Εξαγωγή> Εξαγωγή υλικού-> σήμανση "περιλαμβάνει bitstream"-> OK 3. Εκκίνηση SDK: Αρχείο-> Εκκίνηση SDK.

Βήμα 11: Δημιουργία μονάδας PWM- Δημιουργήστε μια νέα εφαρμογή στο Xilinx SDK

Δημιουργήστε μια νέα εφαρμογή:

Αρχείο> Νέο> Έργο εφαρμογής -> Πληκτρολογήστε το όνομα του έργου σας -> Τέλος

Στο Project Explorer, θα πρέπει να υπάρχουν τρεις φάκελοι.

Σε αυτήν την περίπτωση, "design_1_wrapper_hw_platform_0" είναι ο φάκελος που είχε εξαχθεί προηγουμένως από τη Vivado. Το Axis_2_PWM_SDK_bsp είναι ο φάκελος πακέτων υποστήριξης της πλακέτας. Και το Axis_2_PWM_SDK είναι ο κύριος φάκελος του έργου μας στο SDK. Μπορείτε να δείτε το αρχείο "helloworld.c" κάτω από το φάκελο "src" του Axis_2_PWM_SDK, όπου το "helloworld.c" είναι το κύριο αρχείο.

Βήμα 12: Δημιουργία μονάδας PWM- Επισκόπηση του Project Explorer (I)

Ας ελέγξουμε μερικά αρχεία στο Project Explorer. Αρχικά, στο φάκελο "design_1_wrapper_hw_platform_0", ανοίξτε το "system.hdf". Αυτό το αρχείο δείχνει τον χάρτη διευθύνσεων για τον επεξεργαστή ps7_cortex9 και τα μπλοκ IP που υπάρχουν στο σχεδιασμό μας.

Βήμα 13: Δημιουργία μονάδας PWM- Επισκόπηση του Project Explorer (II)

Στη συνέχεια, ελέγξτε το αρχείο "include" και "libsrc" στο φάκελο "Axis_2_PWM_SDK_bsp". Τα αρχεία βιβλιοθήκης εδώ μας επιτρέπουν να αλληλεπιδράσουμε με περιφερειακά υλικού χωρίς να "παίζουμε" καταχωρητές.

Βήμα 14: Δημιουργία μονάδας PWM- Επισκόπηση του Project Explorer (III)

Μέσω της τεκμηρίωσης BSP, το xtmrctr.h βρίσκεται ως βιβλιοθήκη ελέγχου χρονοδιακόπτη Xilinx που σχετίζεται με το χρονόμετρο AXI. Τυπικά, εδώ θα μπορούσαμε να βρούμε την επιθυμητή συνάρτηση PWM. Ωστόσο, εάν διαβάσετε την τεκμηρίωση "tmrctr_v4_3", δείχνει ότι το πρόγραμμα οδήγησης δεν υποστηρίζει αυτήν τη στιγμή τη λειτουργία PWM της συσκευής. Λόγω της ανεπάρκειας στη λειτουργία PWM, πρέπει να ολοκληρώσουμε τη λειτουργία PWM με τη βοήθεια του xtmrctr.h και του AXI Timer v2.0 LogiCORE IP Product Guide.

Βήμα 15: Δημιουργία μονάδας PWM- Λήψη λειτουργίας PWM (I)

Επιστρέψτε στο κύριο αρχείο "helloworld.c", συμπεριλάβετε τα ακόλουθα αρχεία κεφαλίδας:

Βήμα 16: Δημιουργία μονάδας PWM- Λήψη λειτουργίας PWM (II)

Ορίστε τις βασικές διευθύνσεις δύο AXI TImer μέσω του "xparameters.h".

Βήμα 17: Δημιουργία μονάδας PWM- Λύση λειτουργίας PWM (III)

Δημιουργήστε την επιθυμητή λειτουργία PWM.

Duty_val: μετατρέπει την τιμή βαθμού σε κύκλο λειτουργίας. PWM_Freq_Duty: ορίστε την επιθυμητή συχνότητα και κύκλο λειτουργίας για να δημιουργήσετε PWM. Πρέπει επίσης να οριστεί περίοδος ρολογιού.

PWM_START: εκχωρήστε τη διεύθυνση μητρώου PWM και ξεκινήστε τη δημιουργία PWM.

PWM_STOP: εκχωρήστε τη διεύθυνση μητρώου PWM και σταματήστε τη δημιουργία PWM.

Ο υπόλοιπος κώδικας επίδειξης εμφανίζεται στο "helloworld.c" στην ενότητα "Axis_2_PWM_SDK"

Βήμα 18: Δημιουργία μονάδας PWM- Κάντε το να τρέξει

1. Προγραμματίστε το FPGA μέσω SDK

- Συνδέστε τον πίνακα Zybo μέσω θύρας USB στον υπολογιστή.

- Εργαλεία Xilinx -> Πρόγραμμα FPGA

2. Εκτελέστε το πρόγραμμα

Κάντε κλικ στο εικονίδιο "Εκτέλεση" και αφήστε το μενού -> Εκτέλεση ως -> Εκκίνηση στο υλικό

3. Τερματικό SDK

- Ανοίξτε το τερματικό SDK -> Σύνδεση στη σειριακή θύρα -> OK

- Εκτελέστε το πρόγραμμα. Εάν ο κωδικός επίδειξης εκτελείται με επιτυχία, θα πρέπει να δείτε "Η αρχικοποίηση ολοκληρώθηκε!" στο τερματικό SDK.

Βήμα 19: Επεξεργασία ροής βίντεο σε Digilent ZYBO με OV7670

Επισυνάπτεται το πλήρες αρχείο αρχειοθέτησης.

Βήμα 20: Πλήρες διάγραμμα μπλοκ

Αυτό δείχνει το πλήρες διάγραμμα όλων των συνδέσεων και των μπλοκ IP στο έργο

Βήμα 21: Συνδέστε το OV7670 στο ZYBO

Δημιουργήστε μια σύνδεση για να συνδέσετε τη μονάδα ov7670 στο ZYBO Pmods

Το Data Pmod είναι Pmod D

Το Control Pmod είναι το Pmod C

Επιπλέον, συνδέστε το PmodCON3 και τα servos όπως καθορίζονται στο πρώτο μισό αυτού του σεμιναρίου

Βήμα 22: Δημιουργία Σχεδιασμού Μπλοκ

Στο Flow Navigator, κάντε κλικ στο "Create Block Design" και, στη συνέχεια, πατήστε OK.

Βήμα 23: Προσθέστε αρχεία VHDL για έλεγχο και λήψη φωτογραφικής μηχανής OV7670

Προσθέστε τα αρχεία VHDL που είναι προσαρτημένα σε αυτό το βήμα στο έργο

Βήμα 24: Προσθήκη αρχείου περιορισμών

Προσθέστε το συνημμένο αρχείο περιορισμών στο έργο σας.

Βήμα 25: Προσθέστε IP Repo για HLS IP

Πάρτε το συνημμένο αρχείο Zip και αποσυμπιέστε το σε ένα νέο φάκελο που ονομάζεται παρόμοια σε έναν νέο κατάλογο (φάκελο) που ονομάζεται "HLS_repo".

Προσθέστε ένα αποθετήριο IP στο έργο σας πηγαίνοντας στον κατάλογο IP και κάντε δεξί κλικ επιλέγοντας "Προσθήκη αποθήκης …"

Μεταβείτε στον κατάλογο "HLS_repo" και επιλέξτε τον.

Προαιρετικά: Δημιουργήστε το μπλοκ επεξεργασίας βίντεο HLS για τον εαυτό σας!

Βήμα 26: Προσθέστε ενότητες και IP

Προσθέστε τις ενότητες ov7670_axi_stream_capture, debounce και ov7670_controller στο μπλοκ διάγραμμα κάνοντας δεξί κλικ στο φόντο και επιλέγοντας "Add Module …"

Ομοίως, προσθέστε τα IP:

- HLS_Video_Track

- Ρυθμιστικό καρέ βίντεο εγγραφής

- Ανάγνωση ρυθμιστικού πλαισίου βίντεο

- Ελεγκτής χρονισμού βίντεο

- AXI4-Ροή σε έξοδο βίντεο

- 3 του "Φέτα"

- Συνεχής

- 2 του AXI Timer

Βήμα 27: Ρυθμίσεις διαμόρφωσης IP

Όπως φαίνεται στις εικόνες

Βήμα 28: Προσθήκη και ρύθμιση παραμέτρων του IP IP Block

Προσθέστε το σύστημα επεξεργασίας ZYNQ7 στο μπλοκ διάγραμμα

επεξεργαστείτε τη διαμόρφωση:

-

Διαμόρφωση PS-PL

-

ιπποδύναμη

- Ενεργοποιήστε το S HP 0

- Ενεργοποιήστε το S HP 1

-

-

Διαμόρφωση ρολογιού

-

Ρολόι υφάσματος PL

- FCLK_0 στα 100MHz

- FCLK_1 στα 25MHz (OutputClock)

- FLCK_2 στα 35MHz (<= 50MHz) (CameraClock)

-

Βήμα 29: Μέρος 1. Δημιουργία μονάδας PWM για Servo Motors

Βγάλτε το axi_timer_0 pwm0 στη νέα θύρα εξόδου pwm_Xaxis

Βγάλτε το axi_timer_1 pwm0 στη νέα θύρα εξόδου pwm_Zaxis

Βήμα 30: Πλευρικές συνδέσεις εισόδου βίντεο (επισημαίνεται aclk)

Συνδέστε σωστά τα μπλοκ IP πλευράς εισόδου βίντεο

(* αυτές οι συνδέσεις θα πρέπει να δημιουργηθούν επιλέγοντας τις σωστές επιλογές κατά την αυτοματοποίηση σύνδεσης) "aclk" από το axi_stream_capture πηγαίνει στο:

- ap_clk στην εγγραφή προσωρινής μνήμης πλαισίου βίντεο

- ap_clk στο μπλοκ επεξεργασίας ροής βίντεο HLS

- *aclk στην IP έξυπνης σύνδεσης AXI από το Buffer Video Frame Εγγραφή στο S_AXI_HP0

- *aclk που αντιστοιχεί στα κανάλια της AXI Interconnect IP για τα κανάλια S_AXI του μπλοκ επεξεργασίας βίντεο HLS και το buffer καρέ βίντεο γράψτε S_AXI_HP0_ACLK στο μπλοκ PS

Το σήμα ροής βίντεο συνδέεται απλά σε σειρά από το μπλοκ λήψης στη διεπαφή μνήμης Zynq.

- Το βίντεο μεταβαίνει από το μπλοκ λήψης στο μπλοκ επεξεργασίας HLS.

- Το επεξεργασμένο βίντεο από το μπλοκ HLS πηγαίνει στο μπλοκ εγγραφής του buffer πλαισίου.

- *Το μπλοκ εγγραφής buffer πλαισίου συνδέεται με τη διασύνδεση HP0 στο μπλοκ Zynq PS.

- Το σήμα m_axis_tuser από την έξοδο του μπλοκ λήψης συνδέεται χειροκίνητα τόσο στο σήμα εισόδου video_in_TUSER στο μπλοκ επεξεργασίας HLS όσο και στο σήμα ap_start στο ίδιο μπλοκ.

Το σήμα TUSER (tuser) χρησιμοποιείται από το πρωτόκολλο ροής βίντεο AXI για να δείξει την έναρξη ενός πλαισίου του βίντεο. Το AP_Start λέει στο μπλοκ HLS να ξεκινήσει την επεξεργασία. Χρησιμοποιούμε έτσι το tuser για να ενεργοποιήσουμε το μπλοκ HLS για να επεξεργαστούμε κάθε καρέ όπως εισέρχεται. Όταν συνδέετε ένα μόνο σήμα ενός διαύλου και το διαχωρίζετε με αυτόν τον τρόπο, είναι απαραίτητο επίσης να το συνδέσετε με το κανονικό σημείο τερματισμού του υπόλοιπου διαύλου. Το Vivado υποθέτει ότι εάν συνδέετε το σήμα χειροκίνητα ότι θέλετε να αποσυνδέσετε αυτό στο οποίο θα συνδεόταν κανονικά.

Ρυθμίσεις διαμόρφωσης μπλοκ IP:

Το buffer καρέ βίντεο γράφει:

Μορφές βίντεο: RGB8

1 δείγμα ανά ρολόι Μέγιστες στήλες: 1280 (> = 640) Μέγιστες σειρές: 960 (> = 480) Μέγιστο πλάτος δεδομένων: 8

Βήμα 31: Συνδέσεις στο OV7670

Στο μπλοκ ov7670_axi_stream_capture

- Κάντε όλες τις εισόδους εξωτερικές (κάντε δεξί κλικ σε μια καρφίτσα και επιλέξτε από το μενού ή αριστερό κλικ-> ctrl+T)

- Αφήστε τα ονόματα όπως είναι

Στο μπλοκ ov7670_controller

- Κάντε όλες τις εξόδους μπλοκ εξωτερικές

- Μετονομάστε τη θύρα config_finished σε led0

- συνδέστε το clk με το CameraClock (<= 50MHz) (FCLK_2)

Στο μπλοκ αποκοπής

- συνδέστε την είσοδο button1 σε μια εξωτερική θύρα εισόδου που ονομάζεται btn0

- συνδέστε το out1 στη γραμμή επανάληψης αποστολής στο μπλοκ IP ov7670_controller

- συνδέστε την είσοδο button2 σε μια εξωτερική θύρα εισόδου που ονομάζεται btn3

- συνδέστε το out2n στην είσοδο ext_reset_in στην IP Επαναφορά συστήματος επεξεργαστή για τον τομέα ρολογιού λήψης βίντεο. (*Αυτό μπορεί να χρειαστεί να γίνει μετά τη δημιουργία της IP*)

- συνδέστε το clk με το CameraClock (<= 50MHz) (FCLK_2)

Βήμα 32: Συνδέσεις στο Video Out Side

Συνδέσεις για μπλοκ ελεγκτή χρονισμού βίντεο (VTC), AXI4-Stream to Video Out και φέτες

- Χρησιμοποιήστε ρολόι 25MHz (FCLK_1) για vid_io_out_clk και VTC clk

- Χρησιμοποιήστε ρολόι 100MHz (FCLK_0) για aclk στο AXI4-Stream to Video Out

- vtiming_out σε vtiming_in

- Buffer Video Frame Read M_axis_video πηγαίνει στο AXI4-Stream to Video Out video_in

- Το vtg_ce πηγαίνει στο gen_clken

- Συνδέστε το VTC clken, aclken, vid_io_out_ce με το Constant dout [0: 0]

- Μεταφέρετε το vid_hsync και το vid_vsync σε εξωτερικές θύρες εξόδου vga_hs και vga_vs, αντίστοιχα. (δεν εικονίζεται)

Φέτες:

-

Οι φέτες πρέπει να ρυθμιστούν όπως φαίνεται στις συνημμένες εικόνες

- μετονομάστε τα μπλοκ σε slice_red, slice_green και slice_blue

- Το εύρος ρύθμισης τεμαχίων όπως φαίνεται στις εικόνες ανά όνομα του μπλοκ

- συνδέστε κάθε έξοδο τεμαχίου σε μια έξοδο εξωτερικής θύρας όπως φαίνεται στην εικόνα.

- Το vid_data [23: 0] συνδέεται με τις εισόδους για κάθε φέτα (Din [23: 0])

Βήμα 33: Εκτελέστε Block and Connection Automation

Εκτελέστε Block Automation για να συνδέσετε τα πράγματα από το μπλοκ PS ZYNQ7. Όπως φαίνεται στην εικόνα.

Εκτελέστε την αυτοματοποίηση σύνδεσης για να δημιουργήσετε όλα τα IP διασύνδεσης. Δώστε μεγάλη προσοχή σε όλες τις επιλογές σε κάθε εικόνα.

Στο μπλοκ εξόδου, συνδέστε το out2n στον τομέα ρολογιού λήψης βίντεο Επεξεργασία συστήματος Επαναφορά συστήματος ext_reset_in εισόδου.

Βήμα 34: Δημιουργήστε περιτύλιγμα HDL

Δημιουργήστε το HDL Wrapper για το σχεδιασμό του μπλοκ σας.

Ορίστε το ως την κορυφαία ενότητα.

Βήμα 35: Δημιουργία Bitstream, Εξαγωγή υλικού σε SDK, Εκκίνηση SDK από το Vivado

Βεβαιωθείτε ότι έχετε συμπεριλάβει το bitstream στην εξαγωγή.

Η δημιουργία bitstream μπορεί να διαρκέσει πολύ.

Στη συνέχεια, εκκινήστε το SDK

Βήμα 36: SDK (χωρίς FreeRTOS)

Αυτή η έκδοση κάνει τα πάντα χωρίς να χρησιμοποιεί το FreeRTOS, συμπυκνώνοντας όμορφα τον κώδικα.

Δημιουργήστε ένα αυτόνομο BSP με βάση τον σχεδιασμό υλικού. Οι προεπιλεγμένες επιλογές θα πρέπει να είναι εντάξει. Βεβαιωθείτε ότι έχουν δημιουργηθεί πηγές BSP.

Δημιουργία εφαρμογής όπως φαίνεται στην εικόνα. (κενή εφαρμογή)

Διαγράψτε το κύριο που δημιουργήθηκε αυτόματα και εισαγάγετε τα συνημμένα αρχεία.

Βήμα 37: Εφαρμογή FreeRTOS

Αυτή η έκδοση χρησιμοποιεί το FreeRTOS. Δημιουργήστε ένα BSP FreeRTOS901 με βάση τον σχεδιασμό υλικού. Οι προεπιλεγμένες επιλογές θα πρέπει να είναι εντάξει. Βεβαιωθείτε ότι έχουν δημιουργηθεί πηγές BSP.

Δημιουργία εφαρμογής όπως φαίνεται στην εικόνα. (κενή εφαρμογή)

Διαγράψτε το κύριο που δημιουργήθηκε αυτόματα και εισαγάγετε τα συνημμένα αρχεία.

Βήμα 38: Οδηγίες χρήσης

Αυτό το έργο είναι λίγο δύσκολο να ξεκινήσει. Ακολουθήστε τα βήματα με τη σειρά.

Βεβαιωθείτε ότι το ZYBO δεν φορτώνει τίποτα όταν ενεργοποιείται. Αυτό σημαίνει ότι το LED Done δεν πρέπει να ανάψει. Ένας τρόπος για να γίνει αυτό είναι να ορίσετε το jumper της πηγής εκκίνησης σε JTAG.

Ανοίξτε το έργο (FreeRTOS ή όχι) που θέλετε να προγραμματίσετε από το SDK

- Ενεργοποιήστε το ZYBO σας. Το LED Done δεν πρέπει να ανάψει.

- Προγραμματίστε το FPGA με το αρχείο bit. Το LED Done πρέπει να ανάψει. Το Led0 δεν πρέπει να ανάψει.

- Εκτελέστε τον κώδικα (θυμηθείτε να περάσετε το σημείο διακοπής εκκίνησης εάν το κάνετε αυτό).

Σε αυτό το σημείο θα πρέπει να λαμβάνετε μια έξοδο στην οθόνη VGA.

Για επανεκκίνηση (αν παρουσιάσει σφάλματα ή οτιδήποτε άλλο): πατήστε γρήγορα το κουμπί PS-SRST ή απενεργοποιήστε και μετά ενεργοποιήστε ξανά το ZYBO. Συνεχίστε από το βήμα 2.

Η διακοπή του επεξεργαστή με το πρόγραμμα εντοπισμού σφαλμάτων θα προκαλέσει την κάμερα να κρατήσει τη θέση της αντί να μετακινηθεί. Η ροή βίντεο θα συνεχίσει έτσι κι αλλιώς.

Βήμα 39: Αναφορές και σύνδεσμοι

Οδηγοί αναφοράς και τεκμηρίωση Xilinx:

- PG044 - AXI -Stream to Video Out

- PG278 - Ρυθμιστικό καρέ βίντεο για ανάγνωση/εγγραφή

Άλλοι σύνδεσμοι:

- Το blog του Lauri - εισαγωγή VDMA

- Το blog του Lauri - OV7670 σε έξοδο VGA χρησιμοποιώντας BRAM

- Βικί Hamsterworks, από τον Mike Fields, την αρχική πηγή του κώδικα OV7670

- Φύλλο δεδομένων που δείχνει τις βασικές προδιαγραφές χρονισμού

Συνιστάται:

Η ευκολότερη κάμερα web ως κάμερα ασφαλείας - Ανίχνευση κίνησης και εικόνες με email: 4 βήματα

Η ευκολότερη κάμερα ως κάμερα ασφαλείας - Ανίχνευση κίνησης και εικόνες μέσω ηλεκτρονικού ταχυδρομείου: Δεν χρειάζεται πλέον να κατεβάζετε ή να διαμορφώνετε λογισμικό για να λαμβάνετε εικόνες που εντοπίζονται από την κάμερα στο email σας - απλά χρησιμοποιήστε το πρόγραμμα περιήγησής σας. Χρησιμοποιήστε ένα ενημερωμένο πρόγραμμα περιήγησης Firefox, Chrome, Edge ή Opera σε Windows, Mac ή Android για να τραβήξετε την εικόνα

Upcycled κάμερα εφεδρική κάμερα: 7 βήματα (με εικόνες)

Upcycled Camcorder Backup Camera: Είμαι βέβαιος ότι οι περισσότεροι από εσάς που διαβάζετε αυτό έχετε ένα συρτάρι ή ένα ντουλάπι κάπου γεμάτο από κάποτε αγαπημένη τεχνολογία που μόλις έχει γίνει πολύ παλιά και ξεπερασμένη. Σίγουρα έχω το μερίδιό μου στην παλιά τεχνολογία και είναι λυπηρό να βλέπω τέτοιες δυνατότητες να χάνονται. Λοιπόν, σε αυτόν τον οδηγό, είμαι

Μηχανισμός Pan and Tilt for DSLR Time Lapses: 7 βήματα (με εικόνες)

Μηχανισμός Pan and Tilt for DSLR Time Lapses: Είχα μερικούς βηματικούς κινητήρες και ήθελα πραγματικά να τους χρησιμοποιήσω για να φτιάξω κάτι δροσερό. Αποφάσισα ότι θα φτιάξω ένα σύστημα Pan and Tilt για τη φωτογραφική μηχανή DSLR, ώστε να μπορώ να δημιουργήσω δροσερά χρονικά περιθώρια. Αντικείμενα που θα χρειαστείτε: 2x stepper motors -htt

IOT123 - SOLAR TRACKER - TILT/PAN, PANEL FRAME, LDR MOUNTS RIG: 9 βήματα (με εικόνες)

IOT123 - SOLAR TRACKER - TILT/PAN, PANEL FRAME, LDR MOUNTS RIG: Τα περισσότερα από τα DIY σχέδια για ηλιακούς ιχνηλάτες διπλού άξονα " εκεί έξω " βασίζονται στο 9G Micro Servo που είναι πραγματικά υποτιμημένο για να ωθήσει μερικά ηλιακά κύτταρα, το μικροελεγκτή, την μπαταρία και το περίβλημα. Μπορείτε να σχεδιάσετε γύρω από

Pan-Tilt Multi Servo Control: 11 βήματα (με εικόνες)

Pan-Tilt Multi Servo Control: Σε αυτό το σεμινάριο, θα διερευνήσουμε τον τρόπο ελέγχου πολλών servos χρησιμοποιώντας Python σε Raspberry Pi. Ο στόχος μας θα είναι ένας μηχανισμός PAN/TILT για να τοποθετήσουμε μια κάμερα (ένα PiCam). Εδώ μπορείτε να δείτε πώς θα λειτουργήσει το τελικό μας έργο: Έλεγχος βρόχου Control Servo Control: