Πίνακας περιεχομένων:

- Βήμα 1: Διαμόρφωση Zynq Programmable Logic for Transmitter

- Βήμα 2: Διαμόρφωση Zynq Programmable Logic for Receiver

- Βήμα 3: Εγκατάσταση του προγράμματος οδήγησης VDMA

- Βήμα 4: Ρύθμιση δικτύου Nanorouter

- Βήμα 5: Ρύθμιση συστήματος επεξεργασίας Zynq για μετάδοση δεδομένων μέσω Ethernet

- Βήμα 6: Ρύθμιση συστήματος επεξεργασίας Zynq για λήψη δεδομένων μέσω Ethernet

- Βήμα 7: Συνδέστε τους πίνακες Zybo στην πηγή HDMI και στο νεροχύτη HDMI

- Βήμα 8: Εναλλακτικές ιδέες για βελτίωση

- Βήμα 9: Προσβασιμότητα

- Συγγραφέας John Day day@howwhatproduce.com.

- Public 2024-01-30 08:36.

- Τελευταία τροποποίηση 2025-01-23 14:39.

Θέλατε ποτέ να μπορούσατε να συνδέσετε την τηλεόρασή σας σε υπολογιστή ή φορητό υπολογιστή ως εξωτερική οθόνη, αλλά δεν θέλατε να έχετε όλα αυτά τα ενοχλητικά καλώδια στον δρόμο; Αν ναι, αυτό το σεμινάριο είναι μόνο για εσάς! Ενώ υπάρχουν μερικά προϊόντα που επιτυγχάνουν αυτόν τον στόχο, ένα έργο DIY είναι πολύ πιο ικανοποιητικό και δυνητικά φθηνότερο.

Αυτή η ιδέα διαφέρει από προϊόντα όπως το chromecast, καθώς προορίζεται να αντικαταστήσει ένα καλώδιο HDMI που συνδέεται με μια οθόνη αντί να είναι μια συσκευή ροής.

Το έργο μας δημιουργήθηκε ως ένα τελικό έργο για ένα μάθημα λειτουργικών συστημάτων σε πραγματικό χρόνο στο Πολιτειακό Πολυτεχνικό Πανεπιστήμιο της Καλιφόρνια, San Luis Obispo.

Ο στόχος του έργου είναι να χρησιμοποιήσει δύο πίνακες Digilent Zybo για να λειτουργήσει ως ασύρματη διεπαφή επικοινωνίας μεταξύ συσκευής πομπού HDMI (PC, blu-ray κ.λπ.) σε συσκευή λήψης HDMI (Desktop Monitor, Projector, TV, κ.λπ.).

Το ένα Digilent Zybo θα συνδεθεί μέσω HDMI στη συσκευή εκπομπής και το άλλο θα συνδεθεί μέσω HDMI στη συσκευή λήψης.

Η ασύρματη επικοινωνία θα γίνει με τη χρήση ασύρματου τοπικού δικτύου αφιερωμένου στον πομπό και τον δέκτη, χωρίς να δρομολογείται μέσω οικιακού δρομολογητή ή άλλης τέτοιας συσκευής. Η ασύρματη μονάδα που χρησιμοποιείται για αυτό το έργο είναι ο νανοδιαδρόμος tplink wr802n, ένα από τα οποία λειτουργεί ως σημείο πρόσβασης για τη δημιουργία του δικτύου και το άλλο για να λειτουργεί ως πελάτης για σύνδεση στο δίκτυο. Κάθε νανο δρομολογητής θα συνδεθεί μέσω καλωδίου ethernet σε οποιαδήποτε πλακέτα Zybo. Όταν συνδέονται με αυτούς τους δρομολογητές, οι συσκευές θα επικοινωνούν μέσω TCP σαν να ήταν συνδεδεμένες με ένα μόνο καλώδιο ethernet (που σημαίνει ότι η μόνη διαμόρφωση που απαιτείται για τη δημιουργία μιας σύνδεσης είναι η διεύθυνση IP του προγράμματος -πελάτη).

Ενώ ο στόχος του έργου ήταν να διευκολύνει μια ροή βίντεο 1080x720 @ 60Hz, αυτό δεν ήταν εφικτό λόγω περιορισμών εύρους ζώνης στο ασύρματο δίκτυο και έλλειψης συμπίεσης βίντεο σε πραγματικό χρόνο για μείωση των δεδομένων που απαιτούνται για αποστολή. Αντ 'αυτού, αυτό το έργο χρησιμεύει ως πλαίσιο για μελλοντική ανάπτυξη για την επίτευξη αυτού του στόχου, καθώς έχει περιορίσει σοβαρά τους περιορισμούς στο ρυθμό καρέ για τη σωστή ροή δεδομένων HDMI όπως προβλέπεται.

Απαιτήσεις έργου:

2x Digilent Zybo Development Board (πρέπει να διαθέτουν τουλάχιστον μία θύρα HDMI)

2 x καλώδια HDMI

2x καλώδια microusb (για σύνδεση Zybo με υπολογιστή για ανάπτυξη)

2x νανοδιαδρομείς tplink wr802n (συμπεριλαμβανομένων adtl. 2x προσαρμογείς τροφοδοσίας microusb και πρίζας τοίχου)

2x καλώδια ethernet

*** Σημείωση: Αυτό το σεμινάριο προϋποθέτει εξοικείωση με τη σουίτα σχεδίασης Vivado και εμπειρία δημιουργίας νέου σχεδίου έργου και μπλοκ. ***

Βήμα 1: Διαμόρφωση Zynq Programmable Logic for Transmitter

Η προσέγγισή μας για την ανάπτυξη της προγραμματιζόμενης λογικής του πομπού ήταν να πραγματοποιήσουμε μετάδοση hdmi-to-hdmi από υπολογιστή για παρακολούθηση χρησιμοποιώντας δύο μπλοκ Video Direct Memory Access (VDMA), ένα για εγγραφή και ένα για ανάγνωση.

Και τα δύο είναι επιλεγμένα για ελεύθερη λειτουργία, 3 frame-buffer mode (0-1-2). Δεδομένου ότι ο πυρήνας βίντεο έχει βελτιστοποιηθεί για 60 καρέ ανά δευτερόλεπτο, αυτό σημαίνει ότι το VDMA θα γράφει ή θα διαβάζει σε νέο καρέ κάθε 16,67 ms με αυτή τη σειρά: 0, 1, 2, 0, 1, 2, 0, 1, 2. Οι θέσεις μνήμης DDR για κάθε πλαίσιο είναι διαφορετικές για τα δύο VDMA, επειδή δεν είναι πλέον συγχρονισμένες μεταξύ τους. Αντ 'αυτού, ένας χρονοδιακόπτης υλικού (TTC1), διαμορφωμένος για 60 Hz, χρησιμοποιείται για συγχρονισμό της κίνησης δεδομένων μεταξύ των δύο θέσεων μνήμης.

Η παραπάνω εικόνα δείχνει 3 καρέ, τις διαστάσεις τους και το μέγεθος της μνήμης που απαιτούν το καθένα (στα δεξιά του πλαισίου). Αν εκχωρήσουμε το VDMA εγγραφής σε αυτές τις θέσεις μνήμης, τότε μπορούμε να εκχωρήσουμε τις τοποθεσίες μνήμης VDMA ανάγνωσης πέρα από αυτό το σύνολο, ας πούμε ξεκινώντας με 0x0B000000. Κάθε καρέ αποτελείται από 1280*720 εικονοστοιχεία και κάθε εικονοστοιχείο αποτελείται από 8 μπιτ Κόκκινο, Πράσινο και Μπλε για συνολικά 24 μπιτ. Αυτό σημαίνει ότι ένα πλαίσιο αποτελείται από 1280*720*3 byte (2,76 MB).

Μέσα στο χρονόμετρο IRQ, το οποίο περιγράφεται στη ρύθμιση του προγράμματος οδήγησης VDMA, θα χειριστεί την αντιγραφή δεδομένων μεταξύ των δύο θέσεων μνήμης VMDA. Το VDMA παρέχει έναν δείκτη στο τρέχον πλαίσιο στο οποίο γράφεται ή διαβάζεται. Το πλαίσιο αντιπροσωπεύεται από έναν συγκεκριμένο γκρι κώδικα, ο οποίος μετατρέπεται σε λογισμικό. Οι ορισμοί του γκρι κώδικα για μια διαμόρφωση 3-frame buffer βρίσκονται στον Οδηγό προϊόντων AXI VDMA στο προσάρτημα Γ.

Αυτό μας επιτρέπει να αντιγράψουμε τα περιεχόμενα που γράφονται στη μνήμη χωρίς ανάγνωση από ένα πλαίσιο στο οποίο γράφεται αυτήν τη στιγμή.

*** Σημειώστε ότι το αναγνωσμένο VDMA δεν χρησιμοποιείται κατά την αποστολή δεδομένων μέσω ασύρματου δικτύου. Ο μόνος σκοπός είναι να επαληθεύσει τη σωστή λειτουργία της αντιγραφής μνήμης από το VMDA εγγραφής. Η ανάγνωση του VMDA πρέπει να απενεργοποιηθεί. ***

Ακολουθούν τα βήματα για τη δημιουργία του μπλοκ σχεδίασης πομπού:

- Κατά τη δημιουργία ενός νέου έργου, είναι καλή ιδέα να εκχωρήσετε ένα τσιπ ή πίνακα στο έργο. Αυτός ο σύνδεσμος περιγράφει πώς μπορείτε να προσθέσετε νέα αρχεία πίνακα στον κατάλογο Vivado και να συσχετίσετε τον σωστό πίνακα με το έργο σας. Θα είναι χρήσιμο κατά την προσθήκη του μπλοκ συστήματος επεξεργασίας και τη μετάβαση από υλικό σε λογισμικό (πλευρά SDK).

-

Προσθέστε τα ακόλουθα μπλοκ:

- dvi2rgb

- Βίντεο στο Axi4-stream

- Ελεγκτής χρονισμού

- axi4-stream για έξοδο

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Οδηγός ρολογιού

- Συνεχής

- Σύστημα επεξεργασίας Zynq

- Κατά την προσθήκη του συστήματος επεξεργασίας, κάντε κλικ στην επιλογή "Εκτέλεση αυτοματοποίησης αποκλεισμού" από την επάνω πράσινη έγχρωμη γραμμή και βεβαιωθείτε ότι είναι επιλεγμένη η επιλογή "Εφαρμογή προεπιλογής πίνακα". Αφήστε όλα τα άλλα προεπιλεγμένα.

- Μπορείτε να βρείτε εικόνες από κάθε παράθυρο διαμόρφωσης μπλοκ στις παραπάνω εικόνες. Εάν δεν βλέπετε μια εικόνα για ένα συγκεκριμένο παράθυρο, απλώς αφήστε την ως προεπιλογή.

-

Ξεκινήστε τη διαμόρφωση του συστήματος επεξεργασίας Zynq:

- Σε διαμόρφωση PS-PL AXI Non Secure Enable GP Master AXI, ενεργοποιήστε τη διεπαφή M AXI GP0

- Στη Διαμόρφωση PS-PL HP Slave AXI Interface, ενεργοποιήστε τόσο το HP0 όσο και το HP1

- Στη διαμόρφωση MIO Βεβαιωθείτε ότι το ENET0 είναι ενεργοποιημένο κάτω από περιφερειακά εισόδου/εξόδου, στη συνέχεια, μονάδα επεξεργαστή εφαρμογών, ενεργοποίηση χρονοδιακόπτη0

- Στο Clock Configuration PL Fabric Clocks, ενεργοποιήστε το FCLK_CLK0 και ρυθμίστε το στα 100 MHz.

- Κάντε κλικ στο κουμπί Ok

- Πριν κάνετε κλικ στην επιλογή "Εκτέλεση αυτοματισμού σύνδεσης", βεβαιωθείτε ότι έχετε συνδέσει τα μπλοκ βίντεο, όπως φαίνεται στην παραπάνω εικόνα σχεδιασμού μπλοκ TX. Θα θέλετε να μετονομάσετε τη σταθερά σε VDD και να ορίσετε την τιμή σε 1. Συνδέστε ανάλογα τα μπλοκ βίντεο.

- Κάντε εξωτερικό το ρολόι HDMI TMDS και τις ακίδες δεδομένων στα μπλοκ rgb2dvi και dvi2rgb

- Δημιουργήστε μια θύρα εισόδου και εξόδου για το σήμα ανίχνευσης θερμής πρίζας (HPD) και συνδέστε τα μεταξύ τους, αυτά ορίζονται στο αρχείο περιορισμών

-

Το ρολόι pixel ανακτάται από το TMDS_Clk_p, το οποίο δημιουργείται στο αρχείο περιορισμών. Αυτό θα είναι 74,25 MHz σύμφωνα με την ανάλυση 720p. Είναι σημαντικό να συνδέσετε το ρολόι pixel (από το μπλοκ dvi2rgb) στις ακόλουθες ακίδες:

- vid_io_in_clk (vid in to axi stream block)

- vid_io_out_clk (ροή axi στο μπλοκ vid out)

- clk (Timing Controller)

- PixelClk (rgb2dvi)

- *** Σημείωση: Προς το παρόν, για να ενεργοποιήσετε την ανάκτηση ρολογιού pixel, οι σύνδεσμοι HDMI rx και tx πρέπει να είναι συνδεδεμένοι σε ενεργή πηγή/νεροχύτη. Ένας τρόπος για να το κάνετε αυτό είναι να διαχωρίσετε τα μπλοκ βίντεο rx και tx σε διαφορετικούς τομείς ρολογιού (με άλλα λόγια, δημιουργήστε ένα νέο ρολόι 74,25 MHz για τροφοδοσία στο μπλοκ tx). ***

- Στη συνέχεια, ρυθμίστε τον οδηγό ρολογιού έτσι ώστε να έχετε είσοδο 100 MHz (παγκόσμια πηγή buffer) και 3 ρολόγια εξόδου @ 50 MHz (ρολόι AXI-Lite), 150 MHz (ρολόι AXI4-Stream), 200 MHz (pin dvi2rgb RefClk).

- Συνδέστε το pin του συστήματος επεξεργασίας FCLK_CLK0 στην είσοδο του οδηγού ρολογιού

- Σε αυτό το σημείο κάντε κλικ στην επιλογή "Εκτέλεση αυτοματισμού σύνδεσης" από την πράσινη γραμμή στο επάνω μέρος του παραθύρου σχεδίασης. Είναι καλή ιδέα να το κάνετε αυτό για ένα μπλοκ κάθε φορά και να ακολουθήσετε την παραπάνω εικόνα σχεδιασμού μπλοκ TX.

- Το εργαλείο θα επιχειρήσει να προσθέσει το AXI Interconnect, το οποίο λειτουργεί ως κύρια/δευτερεύουσα διασύνδεση για τα μπλοκ που χρησιμοποιούν το δίαυλο AXI-Lite (VDMA και GPIO).

- Θα προσθέσει επίσης το AXI SmartConnect, το οποίο λειτουργεί ως κύρια/δευτερεύουσα διασύνδεση για τις διεπαφές επεξεργαστή AXI4-Stream και High Performance που χρησιμοποιούνται από το VDMA (Stream to Memory Map και αντίστροφα).

- Το εργαλείο θα προσθέσει επίσης μια Επαναφορά συστήματος επεξεργαστή. Βεβαιωθείτε ότι αυτό είναι συνδεδεμένο μόνο με τα VDMA, GPIO και μπλοκ που σχετίζονται με τον επεξεργαστή. Μην το συνδέετε με κανένα μπλοκ βίντεο (π.χ. dvi2rgb, ελεγκτή χρονισμού, βίντεο σε ροή κ.λπ.)

- Μόλις ολοκληρωθεί η αυτοματοποίηση σύνδεσης, βεβαιωθείτε ότι οι συνδέσεις ταιριάζουν με αυτήν της εικόνας σχεδίασης μπλοκ TX. Θα παρατηρήσετε ένα επιπλέον μπλοκ συστήματος ILA που δεν έχει αναφερθεί. Αυτό είναι μόνο για εντοπισμό σφαλμάτων και δεν χρειάζεται προς το παρόν. Χρησιμοποιεί την Επαναφορά Επεξεργαστή 150M, οπότε ούτε αυτό χρειάζεται. Οπουδήποτε βλέπετε μικρά πράσινα "σφάλματα" στα λεωφορεία, αυτό οφείλεται στο ILA και μπορεί να αγνοηθεί.

- Το τελευταίο βήμα είναι να κάνετε δεξί κλικ στο σχέδιο μπλοκ στο δέντρο πηγών έργου και να επιλέξετε "Δημιουργία περιτυλίγματος HDL". Εάν σκοπεύετε να προσθέσετε λογική στο περιτύλιγμα, θα αντικαθίσταται κάθε φορά που αυτό είναι επιλεγμένο.

- Ανατρέξτε στην ενότητα Ρύθμιση προγράμματος οδήγησης VDMA για λεπτομέρειες στην πλευρά του SDK.

Ρολόγια και Επαναφορά

Έχω διαπιστώσει ότι οι πιο σημαντικές πτυχές κάθε προγραμματιζόμενης λογικής εργασίας είναι η προσεκτική εξέταση των τομέων ρολογιού και η επαναφορά σημάτων. Εάν αυτά είναι σωστά διαμορφωμένα, έχετε μια καλή ευκαιρία να εφαρμόσετε το σχέδιό σας.

Ρολόι Pixel και χρονισμός κλειδωμένο

Για να επαληθεύσετε ότι ορισμένα σήματα είναι ενεργά, είναι καλή ιδέα να συνδέσετε αυτά τα σήματα σε LED (ρολόγια, επαναφορές, κλειδαριές κ.λπ.). Δύο σήματα που βρήκα χρήσιμα για παρακολούθηση στην πλακέτα πομπού ήταν το ρολόι pixel και το σήμα "κλειδωμένο" στο μπλοκ AXI4-Stream to video out, το οποίο σας λέει ότι ο χρονισμός βίντεο έχει συγχρονιστεί με τον ελεγκτή χρονισμού και την πηγή βίντεο δεδομένα. Έχω προσθέσει κάποια λογική στο περιτύλιγμα του μπλοκ σχεδιασμού που παρακολουθεί το ρολόι pixel χρησιμοποιώντας το σήμα PixelClkLocked στο μπλοκ dvi2rgb ως επαναφορά. Έχω επισυνάψει το αρχείο ως hdmi_wrapper.v εδώ. Το αρχείο περιορισμών επισυνάπτεται επίσης εδώ.

Βήμα 2: Διαμόρφωση Zynq Programmable Logic for Receiver

Το μπλοκ προγραμματιζόμενης λογικής για τον δέκτη είναι απλούστερο. Η βασική διαφορά, εκτός από τα μπλοκ εισόδου hdmi που λείπουν, είναι η απουσία ενός ανακτημένου ρολογιού pixel. Για αυτόν τον λόγο πρέπει να δημιουργήσουμε το δικό μας από τον οδηγό ρολογιού. Αυτός ο σχεδιασμός πρέπει να γίνει σε ξεχωριστό έργο από τον πομπό. Για τους σκοπούς μας, το έργο του δέκτη ακολούθησε τον πίνακα Zybo 7Z-20 ενώ ο πομπός ακολούθησε τον πίνακα Z7-10. Τα FPGA στους πίνακες είναι διαφορετικά, οπότε… προσέξτε.

Ακολουθούν τα βήματα για τη δημιουργία του μπλοκ σχεδιασμού δέκτη:

-

Προσθέστε τα παρακάτω μπλοκ ip στο σχέδιό σας:

- Ελεγκτής χρονισμού

- AXI4-Ροή σε έξοδο βίντεο

- RGB σε DVI

- AXI VDMA

- AXI GPIO

- Σύστημα Επεξεργασίας

- Οδηγός ρολογιού

- Σταθερό (το VDD έχει οριστεί σε 1)

- Ακολουθήστε το ίδιο μοτίβο για τη διαμόρφωση αυτών των μπλοκ με τον πομπό. Οι εικόνες για τις αξιοσημείωτες διαφορές στη διαμόρφωση έχουν συμπεριληφθεί εδώ. Οι άλλοι παραμένουν ίδιοι με τον πομπό.

- Διαμορφώστε το VDMA για αυτό το σχέδιο μόνο ως κανάλι ανάγνωσης. Απενεργοποιήστε το κανάλι εγγραφής.

-

Ο οδηγός ρολογιού πρέπει να διαμορφωθεί για τις ακόλουθες εξόδους:

- clk_out1: 75 MHz (ρολόι pixel)

- clk_out2: 150 MHz (ρολόι ροής)

- clk_out3: 50 MHz (ρολόι axi-lite)

- Συνδέστε τα μπλοκ βίντεο, όπως φαίνεται στην εικόνα σχεδιασμού του μπλοκ RX.

- Στη συνέχεια, εκτελέστε την αυτοματοποίηση σύνδεσης, η οποία θα προσθέσει τα μπλοκ AXI Interconnect, AXI SmartConnect και System Reset και θα επιχειρήσει να πραγματοποιήσει τις κατάλληλες συνδέσεις. Πηγαίνετε αργά εδώ για να βεβαιωθείτε ότι δεν εκτελεί ανεπιθύμητες συνδέσεις.

- Κάντε το ρολόι HDMI TMDS και τις ακίδες δεδομένων εξωτερικές στο μπλοκ rgb2dvi

- Δεν χρειάζεται σήμα ζεστού βύσματος σε αυτό το σχέδιο.

Βήμα 3: Εγκατάσταση του προγράμματος οδήγησης VDMA

Η ρύθμιση για τα διαφορετικά μπλοκ που διαμορφώνονται μέσω της διεπαφής AXI-Lite γίνεται καλύτερα χρησιμοποιώντας έργα επίδειξης που περιλαμβάνονται στο BSP ως αναφορά. Μετά την εξαγωγή του υλικού σχεδιασμού και την εκκίνηση του SDK από το Vivado, θα θέλετε να προσθέσετε ένα νέο πακέτο υποστήριξης πλακέτας και να συμπεριλάβετε τη βιβλιοθήκη lwip202 στο παράθυρο ρυθμίσεων BSP. Ανοίξτε το αρχείο αρχείου system.mss από το BSP και θα δείτε τα περιφερειακά προγράμματα οδήγησης που υπάρχουν από το σχεδιασμό του μπλοκ σας. Η επιλογή "Εισαγωγή παραδειγμάτων" σάς επιτρέπει να εισάγετε έργα επίδειξης που χρησιμοποιούν αυτά τα περιφερειακά και σας δείχνουν πώς να τα διαμορφώσετε στο λογισμικό χρησιμοποιώντας τα διαθέσιμα προγράμματα οδήγησης Xilinx (δείτε συνημμένη εικόνα).

Αυτή ήταν η μέθοδος που χρησιμοποιήθηκε για τη διαμόρφωση των VDMA, Timer & Interrupt και GPIO. Ο πηγαίος κώδικας τόσο για τη μετάδοση όσο και για τη λήψη έχει συμπεριληφθεί εδώ. Οι διαφορές είναι σχεδόν αποκλειστικά στο main.c.

*** ΣΗΜΕΙΩΣΗ: Δεδομένου ότι το σύστημα δεν είναι πλήρως λειτουργικό κατά τη σύνταξη αυτού του σεμιναρίου, ο πηγαίος κώδικας σε αυτήν την ενότητα δεν περιλαμβάνει τον κωδικό ασύρματου δικτύου. Αρκετά σφάλματα πρέπει να αντιμετωπιστούν ως αποτέλεσμα του συνδυασμού έργων μετάδοσης/λήψης του πυρήνα βίντεο με έργα μετάδοσης/λήψης δικτύου. Επομένως, αυτό το σεμινάριο τα αντιμετωπίζει ξεχωριστά προς το παρόν. ***

Λειτουργία χειριστή διακοπών TX (IRQHandler)

Αυτή η λειτουργία διαβάζει τους γκρι κώδικες που παρέχονται τόσο από την ανάγνωση όσο και την εγγραφή VDMA μέσω των μπλοκ GPIO. Οι γκρι κώδικες μετατρέπονται σε δεκαδικούς και χρησιμοποιούνται για την επιλογή της θέσης μνήμης βάσης πλαισίου του τρέχοντος πλαισίου. Το πλαίσιο που αντιγράφηκε είναι το προηγούμενο πλαίσιο σε αυτό που γράφτηκε από το VDMA (π.χ. εάν το VDMA γράφει στο πλαίσιο 2, αντιγράφουμε το πλαίσιο 1 · αν γράφουμε στο πλαίσιο 0, τυλίγουμε και διαβάζουμε από το πλαίσιο 2).

Η λειτουργία καταγράφει μόνο κάθε 6ο καρέ για να μειώσει τον ρυθμό καρέ σε 10 Hz αντί για 60 Hz. Το ανώτερο όριο του δικτύου είναι 300 Mbps. Με ταχύτητα 10 καρέ ανά δευτερόλεπτο απαιτείται εύρος ζώνης 221,2 Mbps.

Ο σχολιασμός/η μη σχολιασμός δύο γραμμών σε αυτήν τη λειτουργία θα επιτρέψει στον χρήστη να αλλάξει σε λειτουργία HDMI passthru για σκοπούς εντοπισμού σφαλμάτων/δοκιμών (ο κώδικας σχολιάζεται για να υποδείξει τις κατάλληλες γραμμές). Αυτή τη στιγμή αντιγράφει το πλαίσιο σε μια θέση μνήμης που χρησιμοποιείται από τον κώδικα ethernet.

Λειτουργία χειριστή διακοπών RX (IRQHandler)

Αυτή η λειτουργία είναι πολύ παρόμοια με τη συνάρτηση TX, αλλά αντιγράφει από ένα buffer 2 FIFO που χρησιμοποιείται από το ethernet για την εγγραφή εισερχόμενων δεδομένων. Ο κώδικας ethernet υποδεικνύει σε ποιο πλαίσιο γράφεται το FIFO, τα δεδομένα αντιγράφονται από το αντίθετο πλαίσιο. Τα δεδομένα αντιγράφονται στο πλαίσιο ακριβώς πίσω από αυτό που διαβάζεται από το VDMA για να αποφευχθεί το σχίσιμο.

Βήμα 4: Ρύθμιση δικτύου Nanorouter

Για να δημιουργήσετε ένα δίκτυο χρησιμοποιώντας τους νανο δρομολογητές TPlink, ενεργοποιήστε τους ξεχωριστά και συνδεθείτε στο προεπιλεγμένο SSID wifi για τις συσκευές. Περισσότερες πληροφορίες σχετικά με τις ρυθμίσεις διαμόρφωσης για τη συγκεκριμένη συσκευή μπορείτε να βρείτε μέσω του εγχειριδίου χρήστη της συσκευής.

Ρυθμίστε μία από τις συσκευές ως σημείο πρόσβασης, αυτό θα λειτουργήσει ως η κύρια σύνδεση για το δίκτυο. Βεβαιωθείτε ότι έχετε ονομάσει το δίκτυο και σημειώστε το όνομα και απενεργοποιήστε το DHCP (δεν θέλουμε ο δρομολογητής να ρυθμίζει δυναμικά τις διευθύνσεις IP, θέλουμε οι πίνακες Zybo tansmitter και reciever να ορίσουν οι ίδιοι τις διευθύνσεις IP τους έτσι ώστε να είναι συνεπείς). Μετά τη διαμόρφωση, βεβαιωθείτε ότι η συσκευή επανεκκινείται και δημιουργεί αυτό το δίκτυο.

Ρυθμίστε την άλλη συσκευή ως πελάτη και βεβαιωθείτε ότι συνδέεται με το SSID δικτύου που ρυθμίσατε με τον πρώτο νανο δρομολογητή. Για άλλη μια φορά, βεβαιωθείτε ότι το DHCP είναι απενεργοποιημένο για τον πελάτη.

Μόλις τελειώσει και επανεκκινήσει ο πελάτης, θα πρέπει να συνδεθεί με το νανο δρομολογητή σημείου πρόσβασης (αν δεν το κάνει, πιθανότατα υπάρχει πρόβλημα στη διαμόρφωση μιας από τις συσκευές σας). Θα παρατηρήσετε ότι η λυχνία LED στο πρόγραμμα -πελάτη θα είναι σταθερή μόλις συνδεθεί στο σημείο πρόσβασης.

Το σημείο πρόσβασης nanorouter LED πιθανότατα θα συνεχίσει να αναβοσβήνει σε αυτό το σημείο, αυτό είναι εντάξει! Το φως που αναβοσβήνει σημαίνει ότι δεν είναι συνδεδεμένο με άλλη συσκευή από τη θύρα ethernet και μόλις συνδεθεί σε ένα διαμορφωμένο Zybo, το LED θα παραμείνει σταθερό υποδεικνύοντας μια επιτυχημένη σύνδεση δικτύου.

Τώρα που έχουμε ρυθμίσει τους νανο δρομολογητές μας, έχουμε ένα ασύρματο δίκτυο που θα μας επιτρέψει να επικοινωνούμε μέσω. Μια σημαντική σημείωση είναι ότι η μέθοδος ρύθμισης παραμέτρων για τους νανο δρομολογητές (ως σημείο πρόσβασης και πελάτης) μας επιτρέπει να επικοινωνούμε από τον πίνακα Zybo που εκπέμπει στην πλακέτα Zybo που λαμβάνει σαν να συνδέονταν οι δύο με ένα μόνο καλώδιο ethernet. Αυτό καθιστά τη ρύθμιση του δικτύου μας λιγότερο δύσκολη, καθώς η εναλλακτική λύση θα περιλαμβάνει πιθανώς τη διαμόρφωση των πινάκων Zybo ώστε να συνδέονται ρητά με τον διακομιστή μαζί με την προβλεπόμενη σύνδεση.

Μόλις ρυθμιστούν και οι δύο συσκευές, οι νανοδιαδρομείς έχουν διαμορφωθεί και είναι έτοιμοι να εφαρμοστούν στο δίκτυό σας WIDI. Δεν υπάρχει συγκεκριμένη αντιστοίχιση μεταξύ των νανο δρομολογητών και των πινάκων Zybo, καθώς είτε το σημείο πρόσβασης είτε ο πελάτης θα λειτουργήσει είτε για τη συσκευή μετάδοσης είτε για λήψη.

Βήμα 5: Ρύθμιση συστήματος επεξεργασίας Zynq για μετάδοση δεδομένων μέσω Ethernet

Για να μεταδώσουμε τα δεδομένα HDMI από τη μία πλακέτα Zybo στην άλλη, πρέπει να ενσωματώσουμε ένα πρωτόκολλο Ethernet στο πρόγραμμα οδήγησης VDMA. Ο στόχος μας εδώ είναι να μεταδώσουμε μεμονωμένα πλαίσια βίντεο μέσω του περιφερειακού Ethernet στο σύστημα επεξεργασίας, με καθορισμένο ρυθμό που είναι σύμφωνος με το εύρος ζώνης του δικτύου μας. Για το έργο μας, χρησιμοποιήσαμε το TCP που παρέχεται από το γυμνό μέταλλο LwIP API. Δεδομένου ότι και τα δύο μέλη του έργου είναι σχετικά άπειρα με τα βοηθητικά προγράμματα δικτύωσης, αυτή η επιλογή έγινε χωρίς να αναγνωριστούν πλήρως οι επιπτώσεις και οι περιορισμοί που σχετίζονται με το TCP. Το μείζον πρόβλημα με αυτήν την εφαρμογή ήταν το περιορισμένο εύρος ζώνης και το γεγονός ότι δεν έχει σχεδιαστεί πραγματικά με σκοπό τον ατμό μεγάλου όγκου δεδομένων. Εναλλακτικές λύσεις για την αντικατάσταση του TCP και τη βελτίωση του tbe σε αυτό το έργο θα συζητηθούν αργότερα.

Μια σύντομη περιγραφή του TCP με LwIP: Τα δεδομένα αποστέλλονται μέσω του δικτύου σε πακέτα μεγέθους tcp_mss (μέγιστο μέγεθος τμήματος TCP), το οποίο είναι γενικά 1460 byte. Η κλήση του tcp_write θα λάβει ορισμένα δεδομένα στα οποία αναφέρεται ένας δείκτης και θα ρυθμίσει τις παραμέτρους pbufs (buffer buffet) ώστε να διατηρεί τα δεδομένα και να παρέχει μια δομή για τις λειτουργίες TCP. Ο μέγιστος όγκος δεδομένων που μπορούν να τεθούν σε αναμονή ταυτόχρονα ορίζεται ως tcp_snd_buf (χώρος αποθήκευσης αποστολέα TCP). Δεδομένου ότι αυτή η παράμετρος είναι ένας αριθμός 16 bit, περιοριζόμαστε σε ένα μέγεθος buffer αποστολής 59695 byte (υπάρχει κάποια απαιτούμενη τοποθέτηση στο buffer αποστολής). Μόλις τα δεδομένα έχουν τεθεί σε ουρά, το tcp_output καλείται να ξεκινήσει τη μετάδοση των δεδομένων. Πριν από την αποστολή του επόμενου τμήματος δεδομένων, είναι επιτακτικό ότι όλα τα προηγούμενα πακέτα έχουν μεταδοθεί με επιτυχία. Αυτή η διαδικασία γίνεται χρησιμοποιώντας τη συνάρτηση recv_callback, καθώς αυτή είναι η συνάρτηση που καλείται όταν εμφανίζεται η επιβεβαίωση από τον δέκτη.

Η χρήση των παραδειγμάτων έργων στο Vivado SDK είναι πολύ χρήσιμη για την εκμάθηση του τρόπου λειτουργίας του LwIP TCP και είναι ένα καλό σημείο εκκίνησης για την έναρξη ενός νέου έργου.

Η διαδικασία για τη συσκευή μετάδοσης WiDi έχει ως εξής:

- Αρχικοποιήστε το δίκτυο TCP χρησιμοποιώντας τις κλήσεις λειτουργίας του προγράμματος οδήγησης LWIP γυμνού μετάλλου.

- Καθορίστε τυχόν λειτουργίες επανάκλησης που είναι απαραίτητες για λειτουργίες δικτύου.

- Συνδεθείτε στον δέκτη WiDi συνδέοντας τη διεύθυνση IP και τη θύρα του (η διαμόρφωσή μας: Η διεύθυνση IP του δέκτη είναι 192.168.0.9, συνδεθείτε στη θύρα 7).

- Όταν λήξει ο χρονοδιακόπτης προγράμματος οδήγησης VDMA, εισαγάγετε το TX ISR.

- Καθορίστε την τρέχουσα προσωρινή μνήμη πλαισίου για πρόσβαση βάσει του γκρι κώδικα VDMA

- Βάλτε στην ουρά το πρώτο τμήμα δεδομένων στο buffer αποστολής TCP

- Εξάγετε τα δεδομένα και ενημερώστε τις τοπικές μεταβλητές για να παρακολουθείτε πόσα δεδομένα έχουν αποσταλεί από το τρέχον πλαίσιο.

- Μόλις φτάσετε στη ληφθείσα επανάκληση (η κλήση λειτουργίας πραγματοποιείται αφού ο πομπός λάβει μια επιβεβαίωση ανάκτησης δεδομένων), τοποθετήστε στην ουρά το επόμενο τμήμα δεδομένων.

- Επαναλάβετε τα βήματα 7 & 8 μέχρι να σταλεί ολόκληρο το πλαίσιο.

- Επιστρέψτε σε κατάσταση αδράνειας για να περιμένετε την επόμενη διακοπή του χρονοδιακόπτη για να δείξει ότι ένα νέο πλαίσιο είναι έτοιμο (Επιστροφή στο βήμα 4).

Βεβαιωθείτε ότι έχετε ρυθμίσει τις ρυθμίσεις του LwIP πακέτου υποστήριξης πλακέτας, όπως φαίνεται στην παραπάνω εικόνα. Όλες οι τιμές είναι προεπιλεγμένες εκτός από τα tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Σημειώστε επίσης ότι μπορεί να επιτευχθεί λεπτομερής εντοπισμός σφαλμάτων αλλάζοντας τις παραμέτρους BSP για την ομάδα debug_options.

Βήμα 6: Ρύθμιση συστήματος επεξεργασίας Zynq για λήψη δεδομένων μέσω Ethernet

Ο πίνακας ανάπτυξης Zybo που θα λειτουργεί ως ασύρματος δέκτης θα λειτουργεί παρόμοια με τη συσκευή εκπομπής. Οι ρυθμίσεις πακέτου υποστήριξης πλακέτας για το LwIP θα είναι ίδιες με αυτές του προηγούμενου βήματος.

Η συσκευή θα λάβει πακέτα που περιέχουν τμήματα του πλαισίου βίντεο από το νανο -δρομολογητή και θα αντιγράψει τα δεδομένα των πλαισίων βίντεο στον χώρο προσωρινής μνήμης τριπλού πλαισίου για τον παραλήπτη VDMA. Προκειμένου να αποφευχθεί η αντικατάσταση οποιωνδήποτε δεδομένων, χρησιμοποιείται ένα διπλό buffer δεδομένων (θα αναφερθούμε ως buffer δικτύου) κατά τη συλλογή δεδομένων από το nanorouter, έτσι ώστε η κυκλοφορία του δικτύου να συνεχίσει τη ροή ενώ το προηγούμενο πλήρες πλαίσιο βίντεο αντιγράφεται στο Buffer VDMA.

Η διαδικασία για τη συσκευή λήψης WiDi απαιτεί δύο εργασίες, μία από τις οποίες λαμβάνει δεδομένα ethernet και η άλλη αντιγράφει πλαίσια βίντεο από το buffer δικτύου στο buffer τριπλού πλαισίου του VDMA.

Εργασία λήψης Ethernet:

- Αρχικοποιήστε το δίκτυο TCP χρησιμοποιώντας τις κλήσεις λειτουργίας του προγράμματος οδήγησης LWIP γυμνού μετάλλου (ρύθμιση με διεύθυνση IP στην οποία θα συνδεθεί ο πομπός, 192.168.0.9 στη δική μας)

- Καθορίστε τυχόν λειτουργίες επανάκλησης που είναι απαραίτητες για λειτουργίες δικτύου.

- Μετά τη λήψη πακέτου ethernet, αντιγράψτε τα δεδομένα πακέτων στο τρέχον buffer δικτύου, αυξήστε τα τρέχοντα συσσωρευμένα δεδομένα.

- Εάν το πακέτο γεμίσει το buffer πλαισίου δικτύου, συνεχίστε στα βήματα 5 & 6. Διαφορετικά, επιστρέψτε στο βήμα 3 από αυτήν την εργασία.

- σηματοδοτεί ότι η εργασία αποθήκευσης VDMA τριπλού πλαισίου θα πρέπει να αντιγραφεί από το πρόσφατα τελειωμένο buffer δικτύου.

- Μεταβείτε στο άλλο buffer δικτύου και συνεχίστε να συλλέγετε δεδομένα μέσω ethernet.

- Σε αδράνεια έως ότου ληφθεί νέο πακέτο ethernet (βήμα 3).

Αντιγραφή buffer δικτύου σε VDMA buffer triple frame:

- Όταν λήξει ο χρονοδιακόπτης προγράμματος οδήγησης VDMA, εισαγάγετε το RX ISR.

- Καθορίστε το τρέχον buffer πλαισίου για πρόσβαση με βάση τον γκρι κώδικα VDMA.

- Καθορίστε ποιο buffer δικτύου θα αντιγραφεί στο buffer VDMA και αντιγράψτε αυτά τα δεδομένα

Βήμα 7: Συνδέστε τους πίνακες Zybo στην πηγή HDMI και στο νεροχύτη HDMI

Τώρα συνδέστε τα καλώδια hdmi τόσο για τον δέκτη όσο και για τον πομπό, προγραμματίστε τα FPGA και εκτελέστε το σύστημα επεξεργασίας. Ο ρυθμός καρέ πιθανότατα θα είναι πολύ αργός, λόγω της τεράστιας επιβάρυνσης στη λειτουργία LwIP και του περιορισμένου εύρους ζώνης. Εάν υπάρχουν προβλήματα, συνδεθείτε μέσω UART και προσπαθήστε να εντοπίσετε τυχόν προειδοποιήσεις ή σφάλματα.

Βήμα 8: Εναλλακτικές ιδέες για βελτίωση

Ένα μεγάλο ζήτημα για αυτό το έργο ήταν ο όγκος των δεδομένων που απαιτούνται για την αποστολή μέσω wifi. Αυτό ήταν αναμενόμενο, ωστόσο υποτιμήσαμε τον αντίκτυπο που θα είχε και είχε ως αποτέλεσμα περισσότερο μια έκρηξη εικόνων σε μια οθόνη παρά μια ροή βίντεο. Υπάρχουν διάφοροι τρόποι βελτίωσης αυτού του έργου:

- Συμπίεση βίντεο σε πραγματικό χρόνο. Η συμπίεση της εισερχόμενης ροής βίντεο καρέ -καρέ θα μειώσει σημαντικά τον όγκο των δεδομένων που απαιτούνται για αποστολή μέσω του δικτύου. Ιδανικά αυτό θα γινόταν σε υλικό (κάτι που δεν είναι εύκολη υπόθεση), ή θα μπορούσε να γίνει στο λογισμικό χρησιμοποιώντας τον άλλο πυρήνα ARM για την εκτέλεση αλγορίθμων συμπίεσης (αυτό θα χρειαστεί κάποια περαιτέρω ανάλυση για να διασφαλιστεί ότι ο χρόνος θα τελειώσει). Υπάρχουν ορισμένα στοιχεία συμπίεσης βίντεο σε πραγματικό χρόνο που βρήκαμε στον ιστό, αλλά η πλειοψηφία τους είναι IP.

- Εφαρμογή της ροής Ethernet σε υλικό και όχι λογισμικό. Υπήρχε ένας τόνος γενικών εξόδων λόγω της έλλειψης διαθέσιμου χώρου για την αναμονή εξερχόμενων δεδομένων στον πομπό, λόγω του περιορισμού στο μέγεθος του τμήματος. Μια πολύ πιο αποτελεσματική διαδικασία είναι να χρησιμοποιήσετε το AXI Ethernet IP με ένα FIFO buffer ή DMA για να τροφοδοτήσετε δεδομένα σε αυτό. Αυτό θα μείωνε τις επιπλέον αποσκευές από το LwIP TCP και θα επέτρεπε περισσότερη ροή δεδομένων.

Βήμα 9: Προσβασιμότητα

Το προκύπτον προϊόν αυτού του έργου WiDi θα πρέπει να είναι ένα πλήρως ενσωματωμένο, συμπαγές ζεύγος συσκευών που θα μπορούσε ένας χρήστης να συνδέσει σε οποιαδήποτε πηγή HDMI και στη συνέχεια να βυθίσει την τροφοδοσία βίντεο σε μια οθόνη με δυνατότητα HDMI ασύρματα. Οι συσκευές θα διαθέτουν το Zynq-7000 SoC που βρίσκεται στον πίνακα αναφοράς Zybo και θα ενσωματώνουν το υλικό δικτύου που βρίσκεται στους νανο-δρομολογητές TP-Link. Στην ιδανική περίπτωση, ο χρήστης θα είναι σε θέση να ελέγξει τη μονάδα μετάδοσης από μια διακριτή θέση εντός του λειτουργικού συστήματος στόχου, με μικρή ανάγκη για σημαντική τεχνική ικανότητα.

Ασφάλεια και συνδεσιμότητα

Οι συσκευές θα πρέπει επίσης να ενσωματώνουν την ασφάλεια στρώματος μεταφοράς (TLS) και να έχουν περιορισμένη δυνατότητα αυτόματης σύνδεσης, τόσο για λόγους απορρήτου. Είναι η πρόθεση των σχεδιαστών να κάνουν τη σύνδεση με μια οθόνη μέσω ασύρματης διεπαφής μια σκόπιμη ενέργεια για λογαριασμό του χρήστη για να αποφευχθεί η λανθασμένη μετάδοση ευαίσθητου υλικού.

Παρούσα Κατάσταση

Μέχρι αυτό το σημείο, η κατάσταση του έργου είναι ακόμη πολύ σε εξέλιξη. Προκειμένου ο τρέχων τελικός χρήστης να επωφεληθεί από αυτό το σεμινάριο, πρέπει να έχει μια ισχυρή τεχνική κατανόηση του σχεδιασμού του ενσωματωμένου συστήματος και θα πρέπει να έχει κάποια εξοικείωση με το προγραμματιζόμενο υλικό και το ενσωματωμένο λογισμικό που συνεργάζονται.

Τα δεδομένα που αποστέλλονται μέσω του δικτύου δεν είναι κρυπτογραφημένα σε αυτό το σημείο και θεωρείται ότι είναι μια ακατέργαστη μετάδοση πακέτων TCP/IP.

Το έργο του πυρήνα βίντεο δοκιμάστηκε επιτυχώς τόσο για μετάδοση όσο και για λήψη. Από την άλλη πλευρά, η ασύρματη σύνδεση μεταξύ δύο πλακέτες zybo δημιουργήθηκε και τα δεδομένα του πλαισίου δοκιμής στάλθηκαν με επιτυχία. Ωστόσο, είναι ακόμα απαραίτητο να συνδυαστεί ο κώδικας δικτύου σε κάθε έργο πυρήνα βίντεο και να δοκιμαστεί η μετάδοση των πραγματικών καρέ βίντεο.

Συνιστάται:

Ένας πίνακας ανάπτυξης AVR: 3 βήματα

Ένας πίνακας ανάπτυξης AVR: Το διαδίκτυο είναι γεμάτο έργα με το Arduino. Για λίγο οι πληροφορίες σχετικά με τον μικροελεγκτή ATMEGA328 λείπουν σε όλα τα δεδομένα του Arduino. Αυτό το Insctructable θέλει να ανακτήσει την αρχή του τρόπου ανάπτυξης έργων με χρήση του μικροελέγχου AVR

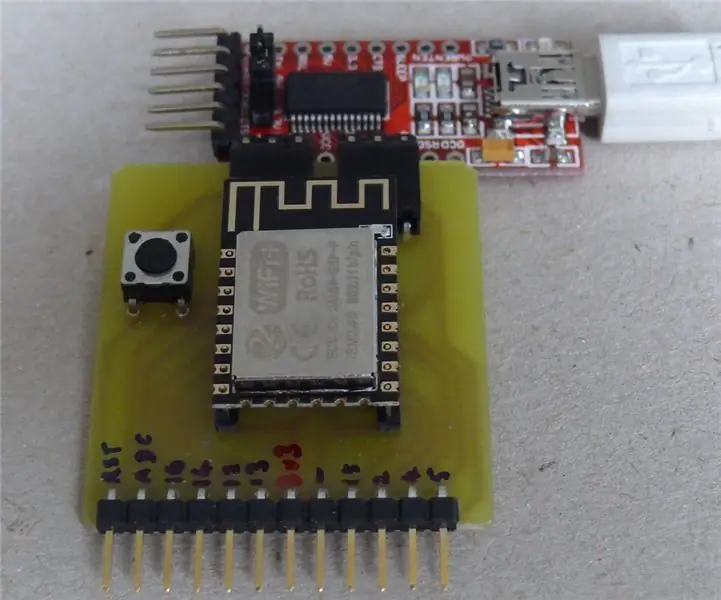

Πίνακας προγραμματισμού και ανάπτυξης ESP-12E και ESP-12F: 3 βήματα (με εικόνες)

Πίνακας προγραμματισμού και ανάπτυξης ESP-12E και ESP-12F: Η εντολή για αυτόν τον πίνακα ήταν απλή: Να μπορείτε να προγραμματίσετε μονάδες ESP-12E και ESP-12F τόσο εύκολα όσο οι πίνακες NodeMCU (δηλαδή δεν χρειάζεται να πατήσετε κουμπιά). Αποκτήστε καρφίτσες φιλικές προς το breadboard με πρόσβαση στις χρήσιμες IO. Χρησιμοποιήστε ξεχωριστό USB για σειριακή μετάδοση

Ο κ. Ε.Ζ. Πίνακας ανάπτυξης σωλήνων: 4 βήματα (με εικόνες)

Ο κ. Ε.Ζ. Tube Development Board: Στόχος/σκοπός: Ο κ. E.Z. Το Tube είναι μια φτηνή πλατφόρμα ήχου σωλήνα κενού χωρίς το «σίδερο»: χωρίς μετασχηματιστή ισχύος, χωρίς μετασχηματιστή εξόδου. Ένας ενισχυτής σωλήνων θα έχει συνήθως αρκετούς βαρύς, ακριβούς μετασχηματιστές: μετασχηματιστές εξόδου που προστατεύουν τα

UDuino: Συμβατός πίνακας ανάπτυξης Arduino με πολύ χαμηλό κόστος: 7 βήματα (με εικόνες)

UDuino: Συμβατός πίνακας ανάπτυξης Arduino με πολύ χαμηλό κόστος: Οι πίνακες Arduino είναι εξαιρετικοί για την πρωτοτυπία. Ωστόσο, γίνονται αρκετά ακριβά όταν έχετε πολλά ταυτόχρονα έργα ή χρειάζεστε πολλούς πίνακες ελεγκτών για ένα μεγαλύτερο έργο. Υπάρχουν μερικές εξαιρετικές, φθηνότερες εναλλακτικές λύσεις (Boarduino, Freeduino), αλλά

Πίνακας Ανάπτυξης Atmega16/32 Με LCD: 8 Βήματα

Πίνακας Ανάπτυξης Atmega16/32 Με LCD: Αυτό το διδακτικό δείχνει, πώς να φτιάξετε τη δική σας πλακέτα ανάπτυξης για τους επεξεργαστές Atmega16 ή Atmega32. Το Διαδίκτυο είναι γεμάτο από οικιακούς πίνακες ανάπτυξης, αλλά νομίζω ότι, υπάρχει χώρος για έναν άλλο. Αυτός ο πίνακας ήταν πολύ χρήσιμος στο έργο μου