Πίνακας περιεχομένων:

- Συγγραφέας John Day day@howwhatproduce.com.

- Public 2024-01-30 08:32.

- Τελευταία τροποποίηση 2025-01-23 14:39.

Το JDM είναι ένας δημοφιλής προγραμματιστής PIC επειδή χρησιμοποιεί σειριακή θύρα, ελάχιστο αριθμό εξαρτημάτων και δεν απαιτεί τροφοδοσία. Υπάρχει όμως σύγχυση εκεί έξω, με πολλές παραλλαγές προγραμματιστή στο δίκτυο, ποιες λειτουργούν με ποιους PIC; Σε αυτό το "διδακτικό" δοκιμάσαμε το JDM και σας δείχνω πώς να προσομοιώσετε το κύκλωμα χρησιμοποιώντας το Spice που θα απαντήσει σε όλες τις ερωτήσεις σας!

Προμήθειες

LTspice το οποίο μπορείτε να κατεβάσετε από τις Αναλογικές Συσκευές εδώ.

Χρειάζεστε επίσης τα αρχεία κυκλώματος JDM εδώ.

Βήμα 1: Απαιτήσεις σειριακής θύρας

Το JDM απαιτεί σειριακή θύρα που πληροί τις προδιαγραφές EIA232, ιδανικά με επίπεδα τάσης +12/-12.

Σύμφωνα με το φύλλο δεδομένων του Texas Instruments Line Driver MC1488 (Εικόνα 3)

Αντίσταση εξόδου = 4V/8mA = 500 ohm.

Όριο ρεύματος βραχυκυκλώματος = 12mV, χωρίς χρονικό περιορισμό - χωρίς ζημιά στο τσιπ.

Αντίσταση εισόδου του δέκτη γραμμής = 3k έως 7k ohm συνιστάται.

Οι σειριακές θύρες σε παλαιότερους επιτραπέζιους υπολογιστές χρησιμοποιούν +12v/-12V που πληρούν αυτήν την απαίτηση.

Οι σειριακές θύρες σε νεότερους φορητούς υπολογιστές χρησιμοποιούν χαμηλότερες τάσεις. Το JDM μπορεί να λειτουργεί ή όχι - η απάντηση είναι πιο περίπλοκη.

Βήμα 2: Απαιτήσεις προγραμματισμού PIC

Πληροφορίες σχετικά με τις απαιτήσεις προγραμματισμού PIC προέρχονται από το Microchip. Τα παραπάνω αφορούν μια τυπική συσκευή.

Βήμα 3: Προδιαγραφή JDM

Έχει χαθεί ο αρχικός ιστότοπος JDM μέσα στην ομίχλη του χρόνου; Αυτό μας αφήνει να μαντέψουμε τι σκόπευε αρχικά ο σχεδιαστής για τις προδιαγραφές.

- Παρέχετε VDD = 5V και έως και IDD = 2mA μέγιστο (για την έκδοση "σε πρίζα")

- Παρέχετε VHH = 13V και έως IHH = 0,2mA μέγιστο.

- MCLR Χρόνος ανόδου tVHHR = 1uS μέγ.

- Η έκδοση ICSP πρέπει να είναι σε θέση να τραβήξει το MCLR χαμηλά έναντι 22k pull-up στο στόχο.

Βήμα 4: Περιγραφή κυκλώματος

Το σχήμα JDM1 βασίζεται στο "τυπικό" κύκλωμα JDM που λαμβάνεται από τον ιστότοπο PICPgm. Αυτός είναι ο προγραμματιστής "PIC in Socket" όπου ο PIC παίρνει ενέργεια από τις ακίδες TX και RTS. Το αρχικό διάγραμμα ήταν δύσκολο να κατανοηθεί, οπότε το ξανασχεδιάζω χρησιμοποιώντας την κανονική σύμβαση της ροής ρεύματος από πάνω προς τα κάτω. Έχω προσθέσει δείκτες LED "RESET", "PROG" και "RTS" που είναι απαραίτητοι κατά την κατασκευή και τις δοκιμές. Ας ελπίσουμε ότι αυτά δεν θα έχουν καμία αρνητική επίδραση στη συμπεριφορά.

Η συνήθης σύμβαση του σχεδιασμού κυκλωμάτων είναι κοινή σε όλους τους τομείς, αλλά το βασικό χαρακτηριστικό του JDM είναι ότι η γειωμένη σειριακή θύρα (GND) συνδέεται με το VDD. Αυτό δημιουργεί σύγχυση καθώς τα σήματα σειριακής θύρας μετρούνται σε σχέση με τα σήματα GND, PIC σε σχέση με το λογικό έδαφος (VSS).

Όταν το TX ανεβαίνει ψηλά, το Q1 συμπεριφέρεται ως δύο μεροληπτικές διόδους προς τα εμπρός. (Ο συλλέκτης Q1 δεν είναι αντίστροφα προκατειλημμένος όπως με την κανονική λειτουργία τρανζίστορ). Ο συλλέκτης Q1 φορτίζει το C2, το οποίο σφίγγεται στο VDD+8V από το Zener (D3). Ο πομπός Q1 παραδίδει 13V στο MCLR για λειτουργία προγράμματος/επαλήθευση.

Όταν το TX μειώνεται, ο πυκνωτής C3 φορτίζεται μέσω D1 και ο VSS σφίγγεται στο VDD-5V με zener (D5). Επίσης το TX σφίγγεται στο (VSS-0,6) από το D1. Το Q1 είναι απενεργοποιημένο, το C1 κρατά τη φόρτιση για τον επόμενο παλμό προγραμματισμού. Το MCLR συσφίγγεται στα 0V με D2, οπότε ο PIC επαναφέρεται τώρα.

Όταν το RTS είναι υψηλό, το ρολόι μεταδίδεται στο PGC. Σφιγκτήρας D4 PGC σε λογική υψηλή VDD. Όταν το RTS είναι χαμηλό, ο πυκνωτής C3 φορτίζεται μέσω D6 και ο VSS σφίγγεται στο VDD-5V με zener (D5). Το D6 σφίγγει το PGC στο VSS ή το λογικό 0.

Κατά τη διάρκεια του προγραμματισμού, τα δεδομένα που αποστέλλονται στο DTR διαβάζονται στο PGD, το οποίο ο PIC ρυθμίζει ως είσοδο. Όταν το DTR είναι υψηλό, το Q2 λειτουργεί ως «ακόλουθος εκπομπών» και η τάση PGD είναι περίπου (VDD-0.6) ή λογική 1. Όταν το DTR είναι χαμηλό, το Q2 λειτουργεί ως κακό τρανζίστορ (οι ακίδες εκπομπής και συλλέκτη αντιστρέφονται). Το Q2 χαμηλώνει το PGD, το οποίο σφίγγεται από το D7 στο VSS ή στο λογικό 0.

Κατά τη διάρκεια της επαλήθευσης, ο PIC ρυθμίζει το PGD ως έξοδο για την αποστολή δεδομένων στη σειριακή θύρα. Το DTR πρέπει να είναι υψηλό και τα δεδομένα διαβάζονται στο CTS. Όταν η έξοδος PGD είναι υψηλή, το Q2 είναι απενεργοποιημένο, CTS = DTR = +12V. Όταν η έξοδος PGD είναι χαμηλή, το Q2 είναι ενεργοποιημένο. Ο συλλέκτης Q2 αντλεί ρεύμα (12V+5V)/(1k+1k5) = 7mA από το DTR και τραβάει το CTS χαμηλά, στο VSS.

Βήμα 5: Προετοιμαστείτε για προσομοίωση

Κατεβάστε το μπαχαρικό LT, αποθηκεύστε και ανοίξτε τα αρχεία κυκλώματος (*.asc) που παρέχονται εδώ. Για να προσομοιώσουμε το κύκλωμα, πρέπει να του δώσουμε κάποιες εισόδους και μετά να «εντοπίσουμε» τις εξόδους. V1, V2 V3 προσομοιώνουν τη σειριακή θύρα 12V με σύνθετη αντίσταση εξόδου R11, R12, R13.

- Το V1 δημιουργεί 2 παλμούς προγράμματος σε TX από 0,5ms έως 4,5ms

- Το V2 δημιουργεί έκρηξη παλμών δεδομένων στο DTR από 1,5 έως 4,5ms

- Το V3 δημιουργεί εκρήξεις παλμών ρολογιού στο RTS από 0,5 έως 3,5ms

Τα συστατικά V4, X1, R15 και R16 είναι όλα μέρος της προσομοίωσης.

- Το V4 παράγει 2 παλμούς από 2,5 έως 4,5 ms για επαλήθευση δεδομένων.

- Το Jumper X1 προσομοιώνει το OUTPUT στο PGD.

- Τα R15, R16 προσομοιώνουν τη "φόρτωση" του PIC σε VDD και MCLR.

Βήμα 6: Τροποποιήσεις για το ICSP

Το σχήμα JDM3 δείχνει την έκδοση για προγραμματισμό "in circuit". Οι τροποποιήσεις από το αρχικό είναι

- Αντικαταστήστε την υποδοχή ZIF με υποδοχή ICSP.

- Ο PIC τροφοδοτείται τώρα από κύκλωμα τροφοδοσίας -στόχου (V5).

- Αφαιρέστε 5V zener (D5).

- Ο μικρός πυκνωτής 100pF (C4) μετακινείται δίπλα στο PIC στο κύκλωμα στόχου.

- Οι λυχνίες LED παίρνουν ενέργεια από την πλακέτα κυκλώματος όπου είναι δυνατόν.

- Η αντίσταση έλξης MCLR (R10) και η δίοδος (D10) απαιτούνται στο κύκλωμα στόχου.

- ΠΡΟΕΙΔΟΠΟΙΗΣΗ. Ο πίνακας προορισμού πρέπει να έχει μια "πλωτή" παροχή, ιδανικά μια μπαταρία.

- Μην συνδέετε γείωση στόχου (VSS) με γείωση υπολογιστή/υπολογιστή συνδέοντας άλλες θύρες υπολογιστή ταυτόχρονα με το JDM.

Μετά την προσομοίωση του JDM1, το πρόβλημα του μεγάλου χρόνου φόρτισης στο C2 έγινε εμφανές. Στη συνέχεια, μετά την ανάγνωση του Fruttenboel φαίνεται ότι τα C2 και Q1 προστέθηκαν ως τροποποίηση στο πρωτότυπο. Δεν μπορώ να σκεφτώ τι προορίζονται να κάνουν τα C2 και Q1 εκτός από τη δημιουργία προβλημάτων. Έτσι, για το JDM4, επιστρέφουμε στον παλαιότερο σχεδιασμό του Fruttenboel, ο οποίος είναι απλός και κατανοητός. Σφιγκτήρας D1 και D3/LED2 MCLR μεταξύ VSS και VDD+8V. Η τιμή του R1 μειώνεται στα 3k3, αρκεί για να φωτίσει το LED2 στα 12V.

Το JDM4 έχει επίσης σχεδιαστεί για να λειτουργεί με ασθενέστερες σειριακές θύρες. Όταν το TX ανεβαίνει υψηλά (+9V), πηγή ρεύματος TX = (9-8)/(1k +3k3) = 0.2ma, ίσα ίσα για να τραβήξει το MCLR ψηλά, αν και ανεπαρκές για να φωτίσει το LED2. Όταν το TX μειώνεται (περίπου -7V), ο νεροχύτης του TX = (9-7)/1k = 2mA. Ρεύμα LED1 ((7-2 για led)/(2k7) = 1,8mA. MCLR έλξης προς τα κάτω ρεύμα = 7-5.5/3k3 = 0.5mA.

Αυτό το κύκλωμα έχει επίσης δοκιμαστεί (προσομοίωση JDM5) για να δει τι συμβαίνει με τις σειριακές θύρες +/- 7V ελάχιστο, όπου δεν υπάρχει επαρκής τάση για να διατηρηθεί VHH = 13V. Ο σκοπός του C1 τώρα γίνεται προφανής, το C1 δημιουργεί μια σύντομη +ve ώθηση στο MCLR, μια αύξηση 33us στην ανερχόμενη άκρη του TX, αρκετά μεγάλη για να μπορέσει ο PIC να εισέλθει σε λειτουργία προγραμματισμού, ίσως; Αλλά αφαιρέστε το βραχυκυκλωτήρα X2 (απενεργοποιήστε το LED1) καθώς δεν υπάρχει αρκετό ρεύμα για να χαμηλώσει το MCLR και να φωτίσει το LED1 μαζί. Όταν το TX πέφτει χαμηλά, ο νεροχύτης TX = (7V-5.5V)/(1k+3k3) = 0.3mA, αρκεί μόνο για να τραβήξει χαμηλά το MCLR έναντι του ανασυρόμενου R10.

Βήμα 7: Αποτελέσματα προσομοίωσης

Για να δείτε τα γραφικά αρχεία, είναι προτιμότερο να κάνετε δεξί κλικ στους παρακάτω συνδέσμους και μετά να επιλέξετε "Άνοιγμα συνδέσμου στη νέα καρτέλα"

Προσομοίωση 1: ίχνος MCLR, VSS και RTS για το αρχικό JDM1. Αμέσως παρατηρούνται οι παρατηρήσεις 1, 2 και 3.

Προσομοίωση 2: ίχνος MCLR και VSS και RTS για τροποποιημένο JDM2, το οποίο διορθώνει προηγούμενα προβλήματα.

Προσομοίωση 3: ίχνος PGD, VSS και PGC για αποστολή δεδομένων JDM2 σε λειτουργία προγράμματος. Παρατήρηση 4 στα 3,5 mS.

Προσομοίωση 4: ίχνος PGD, VSS και CTS για JDM2 σε λειτουργία επαλήθευσης (έχει τοποθετηθεί ο βραχυκυκλωτήρας X1). Εντάξει

Προσομοίωση 5: ίχνος MCLR, VSS, PGD και PGC για JDM3. Το ICSP που χρησιμοποιεί ισχύ από το κύκλωμα επιλύει πολλά προβλήματα.

Προσομοίωση 6: ίχνος MCLR, VSS, PGD και PGC για JDM4 με σειριακή θύρα +/- 9V. Το MCLR ανεβαίνει αμέσως, λειτουργεί πλήρως.

Προσομοίωση 7: ίχνος MCLR, VSS και TX για JDM5 με σειριακή θύρα +/- 7V και jumper X2 που έχουν αφαιρεθεί. Το C1 δημιουργεί μια αύξηση +ve (άνοδο) στην ανερχόμενη άκρη του MCLR, σχεδόν επαρκής για να ωθήσει το MCLR πάνω από το TX στα 13V.

Βήμα 8: Συμπεράσματα

Το Spice είναι πολύ καλό στην αποκάλυψη των «κρυφών μυστικών» της λειτουργίας του κυκλώματος. Προφανώς το κύκλωμα JDM λειτουργεί και είναι συμβατό με πολλά τσιπ PIC, αλλά οι ακόλουθες παρατηρήσεις αποκαλύπτουν πιθανούς περιορισμούς/ζητήματα συμβατότητας/βλάβες;

- Χρόνος μεγάλης ανόδου του MCLR ενώ το C2 χρεώνεται στο VPP στον πρώτο παλμό του TX. Αποτυγχάνει η προδιαγραφή 3.

- Η σειριακή θύρα χρεώνει το C2 όταν το TX ανεβαίνει ψηλά και το RTS χαμηλώνει. Αλλά το RTS έχει επίσης τη δουλειά της φόρτισης του C3. Όταν συμβαίνουν και τα δύο ταυτόχρονα, αυτό δημιουργεί περισσότερο φορτίο στο RTS, συνεπώς το C3 χάνει το φορτίο (το VSS αυξάνεται) στα 2ms κατά την προσομοίωση. Αποτυγχάνει η προδιαγραφή 1.

- Το C3 χάνει τη φόρτιση (το VSS αρχίζει να ανεβαίνει) αφού οι παλμοί του ρολογιού σταματήσουν στα 3,5ms.

- Ποιος είναι ο σκοπός του C2, χρειάζεται καθόλου;

Λύσεις

- Πιθανότατα το PICPgm χρησιμοποιεί ένα λογισμικό "round-round". Πρέπει να εφαρμόσει έναν μακρύ παλμό TX για να προφορτίσει στο C2, και μετά να εισέλθει στη λειτουργία προγραμματισμού μόνο μετά τον δεύτερο παλμό TX; Για προσομοίωση μείωσα την τιμή του C2 σε 1uF για να δώσω χρόνο ανόδου 1ms. Δεν είναι ιδανική λύση.

- Διαχωρίστε τα C2 και C3 ώστε να φορτίζονται ανεξάρτητα. Μια μικρή τροποποίηση στο JDM2, το C2 αναφέρεται στο GND αντί του VSS.

- Λύθηκε με JDM3. Το ICSP είναι πολύ πιο αξιόπιστο καθώς το PIC τροφοδοτείται από κύκλωμα στόχου.

- Το JDM4 λύνει το πρόβλημα 1. Αυτός είναι ένας απλός σχεδιασμός που εξαλείφει εντελώς το C2.

Βήμα 9: Και τέλος

Η απόδειξη της πουτίγκας είναι στο φαγητό. Αυτό το JDM λειτουργεί οπότε συνεχίστε να το χρησιμοποιείτε.

Και οι προτάσεις μου είναι:

- χρησιμοποιήστε το JDM2 για προγραμματισμό υποδοχών και σειριακές θύρες 12V,

- χρήση JDM4 για προγραμματιστή ICSP και σειριακές θύρες πάνω από +/- 9V,

- χρησιμοποιήστε JDM4 με το jumper X2 που έχει αφαιρεθεί για σειριακές θύρες άνω των +/- 7V.

Βιβλιογραφικές αναφορές:

Αναλογικές συσκευές μπαχαρικό LT

picpgm

Fruttenboel

Ακολουθήστε περισσότερα έργα PIC στο sly-corner

Συνιστάται:

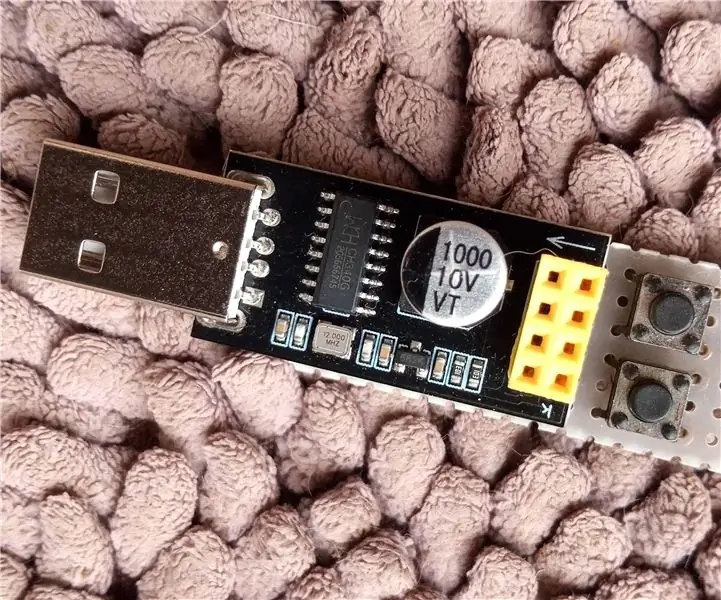

ESP -01 Hack Programmer - The Easy One :): 6 βήματα

ESP-01 Hack Programmer-The Easy One :): Γεια σας ESPers, Σε αυτό το διδακτικό θα σας δείξω ένα απλό hack για να κάνετε προγραμματιστή για την ενότητα ESP-01 / ESP8266-01 / ES-01. Οι περισσότεροι από εμάς έχουμε χρησιμοποιήσει έναν πίνακα Arduino ή συσκευές FTDI USB-TTL ως προγραμματιστές για αυτήν την ενότητα. Και οι δύο μέθοδοι λειτουργούν καλά. Αλλά τ

Πώς να κάνετε Flash ή να προγραμματίσετε το ESP8266 AT Firmware χρησιμοποιώντας το ESP8266 Flasher και Programmer, IOT Wifi Module: 6 Βήματα

Πώς να φλας ή να προγραμματίσετε το ESP8266 AT Firmware χρησιμοποιώντας το ESP8266 Flasher και Programmer, IOT Wifi Module: Περιγραφή: Αυτή η μονάδα είναι προσαρμογέας /προγραμματιστής USB για μονάδες ESP8266 τύπου ESP-01 ή ESP-01S. Είναι βολικά εξοπλισμένο με γυναικεία κεφαλίδα 2x4P 2,54mm για να συνδέσετε το ESP01. Επίσης, σπάει όλες τις ακίδες του ESP-01 μέσω αρσενικού 2x4P 2,54mm

(σχεδόν) Universal MIDI SysEx CC Programmer (and Sequencer ): 7 βήματα (με εικόνες)

(σχεδόν) Universal MIDI SysEx CC Programmer (και Sequencer …): Στα μέσα της δεκαετίας του ογδόντα οι παραγωγοί synths ξεκίνησαν ένα " λιγότερο είναι καλύτερο " διαδικασία που οδήγησε σε ξυλόσπονδα synths. Αυτό επέτρεψε τη μείωση του κόστους από την πλευρά του κατασκευαστή, αλλά έκανε τη διαδικασία επιδιόρθωσης κουραστική αν όχι αδύνατη για την τελική χρήση

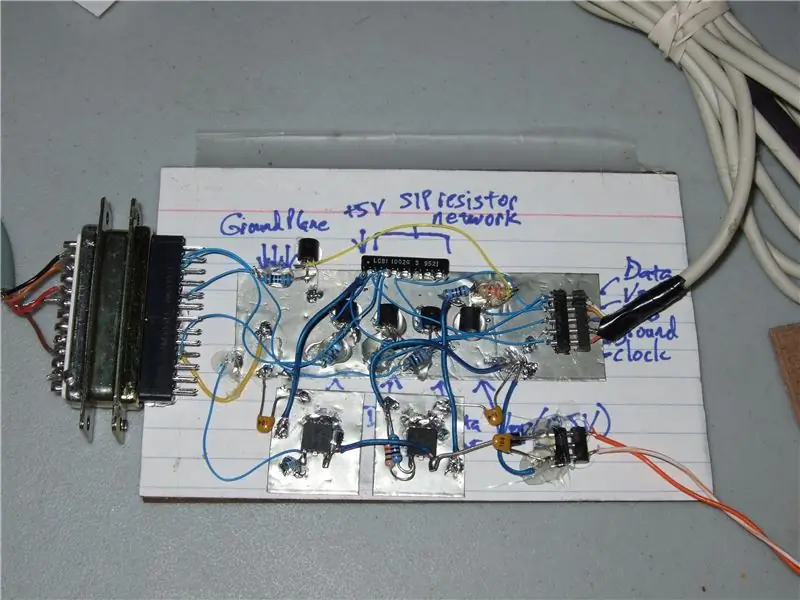

5 Transistor PIC Programmer *Σχηματική προσθήκη στο βήμα 9 !: 9 βήματα

5 Transistor PIC Programmer *Σχηματική προσθήκη στο βήμα 9 !: Φτιάξτε το δικό σας προγραμματιστή PIC για την παράλληλη θύρα του υπολογιστή σας. Αυτή είναι μια παραλλαγή του κλασικού σχεδιασμού του David Tait. Είναι πολύ αξιόπιστο και υπάρχει καλό λογισμικό προγραμματισμού διαθέσιμο δωρεάν. Μου αρέσει ο προγραμματιστής IC-Prog και PICpgm. Το καλύτερο από όλα, είναι

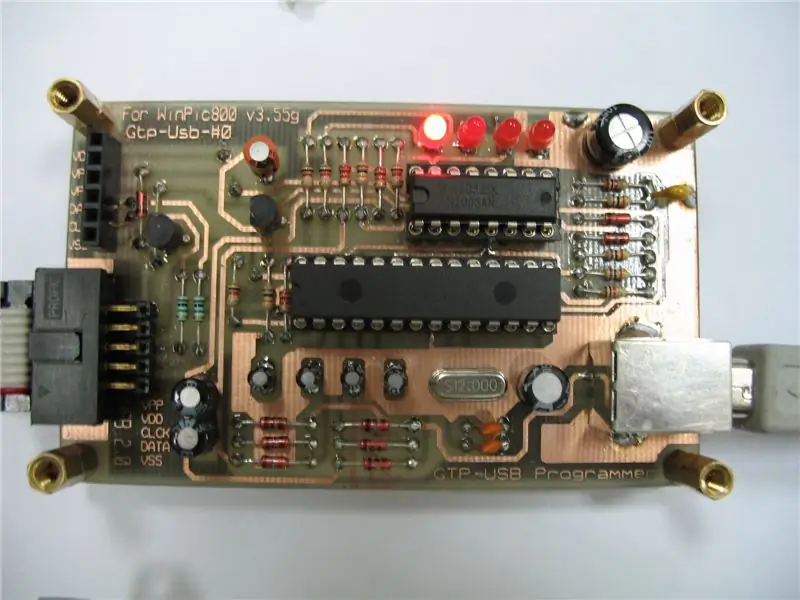

GTP USB PIC PROGRAMMER (Open Source): 5 βήματα (με εικόνες)

GTP USB PIC PROGRAMMER (Open Source): Αυτή η εργασία περιλαμβάνει, GTP USB (όχι plus ή lite). Το σχήμα, οι φωτογραφίες και το PCB έχουν αναπτυχθεί από την PICMASTERS με βάση μερικά πολύτιμα έργα που έχουν γίνει στο παρελθόν. Αυτός ο προγραμματιστής υποστηρίζει pic10F, 12F, 16C, 16F, 18F, 24Cxx Eeprom. Δυστυχώς, έγινε