Πίνακας περιεχομένων:

- Συγγραφέας John Day day@howwhatproduce.com.

- Public 2024-01-30 08:38.

- Τελευταία τροποποίηση 2025-01-23 14:39.

Bienvenue dans notre projet Autotune

Notre équipe va vous présenter la réalisation de ce projet. Notre équipe est composée de 3 élèves ingénieurs de Polytech Sorbonne en EISE4 (4ème année du cycle ingénieur en électronicque informatique systèmes embarqués).

Notre projet συνίστανται στο émettre un son capter par un micro, το émit par un haut parleur et afficher la FFT sur un écran PC. Il sera possible de modifier le son audio comme le volume et créer un écho.

C'est parti pour les επεξηγήσεις !!

Βήμα 1: Χρήση συνθέτων

- Carte DEO-Nano-SoC

- Μπαταρία 2 έξοδος à 5V2A

- Μικρο

- Haut Parleur 8 Ohm

- Ρυθμιστής: MAX660

- Capteur IR: GP2Y0E02A

- Pχος Ampli: LM386N-1/NOPB

- DAC: MCP4821-E/P

- Δίοδος: 1N4148

- Transitor: LND150N3-G / N-FET

- 2 AOP: TL081C

- Αντιστάσεις

- Συμπυκνωτές

- Wifi: ESP8266EX

- 4 διακόπτες

- 3 Leds de couleurs

Βήμα 2: Αρχιτεκτονική

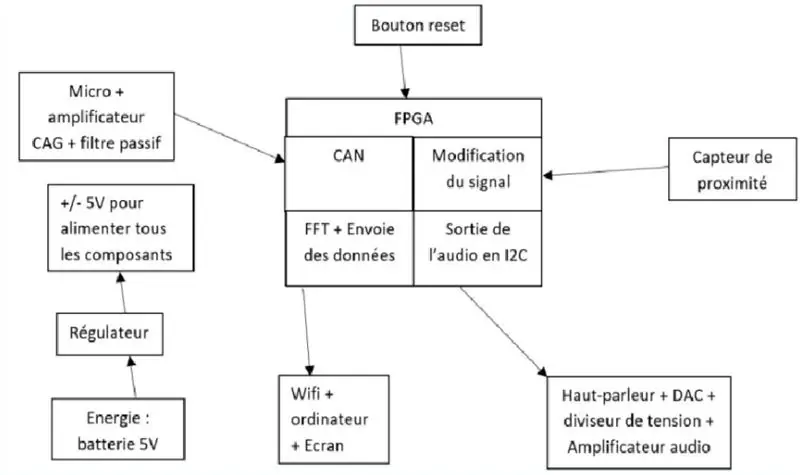

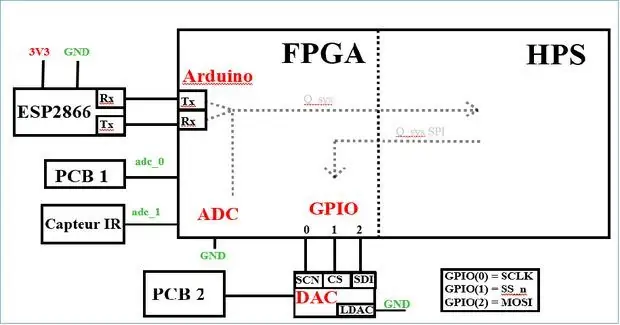

Voici ci-dessus notre schéma bloc représentant l'architecture de notre projet Autotune.

Comme vous pouvez le voir, notre projet va pouvoir capter un son à l'aide du micro dont le signal analogique capté sera converti en un signal numérique dont l'ADC is intégré dans la carte FPGA. Puis le signal sera modifié selon nos effets choisis à l'aide d'un capteur de proximité et des switchs. Enfin, le signal modifié depuis la carte sera reconverti en un signal analogical and sera transmise à travers le haut parleur.

Βήμα 3: Partie Analogique

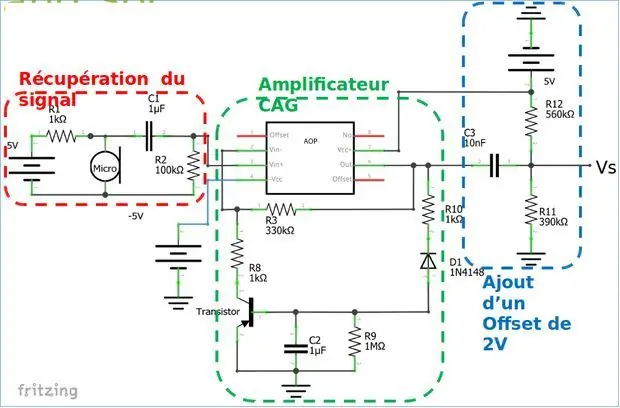

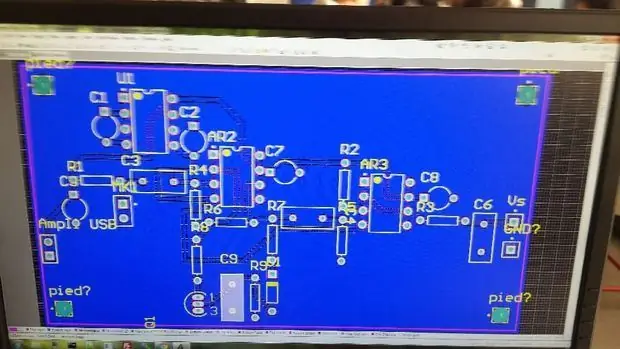

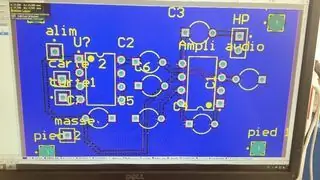

Notre partie analogie est composée de 2 κυκλώματα:

Un Premier circuit qui représentera la partie micro, qui sera branché au CAN de la carte FPGA, composé d'un amplificateur de gain et d'un filtre passif après avoir récupérer le signal.

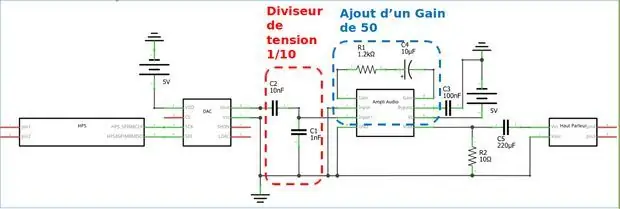

Unux deuxieme circuit qui repésentera la partie haut parleur, qui sera branché à la sortie de la carte FPGA, composé du DAC, d'un diviseur de tension et d'un amplificateur audio.

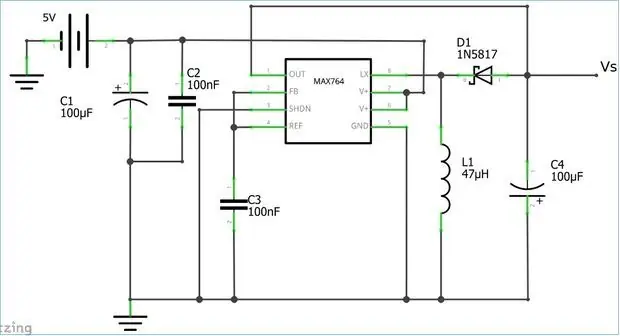

Le troisième schéma est celui du régulateur produisant du -5V pour alimenter tous les compositors.

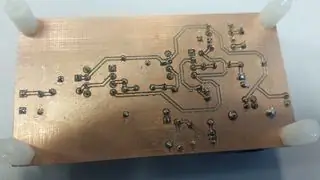

Βήμα 4: Impression Des PCB

Συντηρητικό, nous allons créer nos PCB afin de les imprimer et de les relier!

A l'aide du logiciel Alitum, nous avons pu creer deux PCBs, c'est à dire la partie micro et haut parleur. Voici le site ανταποκριτής ή tutoriel Altium qui peut sureement vous aider!

Βήμα 5: Partie Numérique

Après avoir imprimer vs PCB, vous pouvez enfin brancher le tout à la carte FPGA!

Pour la partie numérique, nous avons créer un code C qui est séparé en deux en utilisant un thread. D'un coté, on récupère le signal on le modifie et on l'envoie vers le DAC en spi. D'un deuxième côté, on calcule la fft et on envoie le résultat par wifi. Cette séparation permet d'éviter les ralentissements sur la première partie.

Κατά τη χρήση Qsys et quartus pour brancher le HPS avec les différents συνθετικά. On use notamment une IP SPI pour communiquer avec le dac et une IP UART pour communiquer avec la carte wifi.

Βήμα 6: Le Code

Voici le lien où nous avons récuperé le code pour faire la fft.

Κατά τη χρήση του κώδικα pour calculler la fft:

// Création de la configuration et des buffers in et out pour s (t) et S (f) const kiss_fft_cfg config = kiss_fft_alloc (NFFT, 0, NULL, NULL);

kiss_fft_cpx*in = (kiss_fft_cpx*) malloc (NFFT*sizeof (kiss_fft_cpx)); kiss_fft_cpx*out = (kiss_fft_cpx*) malloc (NFFT*sizeof (kiss_fft_cpx));

για (j = 0; j <NFFT; j ++) {Τιμή = *h2p_lw_adc_addr; // recupère la valeur provenant du pcb du microin [j].r = Τιμή-2000.0; // on pension l'offset de cette valeurfor (i = 0; i <2100; i ++) {} // παρακολουθήστε un temps bien précis pour avoir une fréquence d’échantillonnage connue}

// Calcul de la FFT depuis in vers outkiss_fft (config, in, out); bzero (C_val, 110); // remet à zero le tableau qui nous sert de buffer que l'on va envoyer par wififor (t = 0; t <(NFFT/4); t ++) {// pour limiter la taille du buffer on limite la sortie de la fft à des valeurs entre 0 et 9 tmp_log = 20*(log (abs (out [t].r/1000.0))))*9;

tmp_log = tmp_log/50; αν (tmp_log <0) {tmp_log = 0; } if (tmp_log> 9) {tmp_log = 9; } sprintf (tmp_val, "%d", tmp_log); strcat (C_val, tmp_val); // ajoute au buffer la nouvelle valeur

} send_wifir (C_val); // on envoi le buffer par wifi

fonction send wifir:

void send_wifir (char* com_AT) {int num, z; για (z = 0; z <22000000; z ++) {} για (num = 0; num <(int) strlen (com_AT); num ++) { *(h2p_lw_rs232_addr) = com_AT [num]; }}

Ρίξτε αρχικοποιητή la carte wifi στο use le suivant:

send_wifi ("AT+RST / r / n"); // demande de reset à la cartesleep (3); // παρακολουθήστε qu'elle resetsend_wifi ("AT+CWMODE = 3 / n / r"); // επιλέξτε τη λειτουργία de la cartesend_wifi ("AT+CWJAP = \" wifiNom / ", \" MotDePasse / "\ r / n"); // on lui demande de se connecter ή wifisleep (15); // σχετικά με την παρουσία qu'elle se connectesend_wifi ("AT+CIPSTART = \" UDP / ", \" 192.168.43.110 / ", 32003 / r / n"); // On lui demande de se connecter en udp avec le serveur ouvert sur un autre ordinateursleep (3); // παρακολούθηση la connexionsend_wifi ("AT+CIPMODE = 1 / r / n"); // on se met en mode envoie en συνεχίζει τον ύπνο (3); send_wifi ("AT+CIPSEND / r / n"); // κατά την έναρξη της μετάδοσης

fonction send wifi:

void send_wifi (char * com_AT) {int num, z; for (num = 0; num <(int) strlen (com_AT); num ++) { * (h2p_lw_rs232_addr) = com_AT [num]; για (z = 0; z <2500000; z ++) {}}}

Κωδικός υπηρεσίας:

affichage de la fft:

int i, j, Τιμή = 0; σύστημα ("σαφές")?

για (i = 0; i <41; i ++) {if (i <40) {for (j = 0; j <BUFSIZE; j ++) {if (table [j]*4> (40 - i)) {if (πίνακας [j]*4> 35) printf (RED "|" RESET); αλλιώς εάν (πίνακας [j]*4> 28) printf (L_RED "|" RESET); αλλιώς εάν (πίνακας [j]*4> 21) printf (YEL "|" RESET); else if (πίνακας [j]*4> 14) printf (L_YEL "|" RESET); αλλιώς εάν (πίνακας [j]*4> 7) printf (L_GRN "|" RESET); else printf (GRN "|" RESET); } else printf (""); } printf ("\ n"); } else {printf ("0Hz 2,5Hz 5Hz 7,5kHz 10kHz / n"); /*για (j = 0; j <(BUFSIZE/2); j ++)

Συνιστάται:

Πώς να φτιάξετε 4G LTE Double BiQuade Antenna Εύκολα Βήματα: 3 Βήματα

Πώς να κάνετε εύκολα 4G LTE διπλή κεραία BiQuade Antenna: Τις περισσότερες φορές αντιμετώπισα, δεν έχω καλή ισχύ σήματος στις καθημερινές μου εργασίες. Ετσι. Searchάχνω και δοκιμάζω διάφορους τύπους κεραίας αλλά δεν δουλεύω. Μετά από σπατάλη χρόνου βρήκα μια κεραία που ελπίζω να φτιάξω και να δοκιμάσω, γιατί δεν είναι η βασική αρχή

Σχεδιασμός παιχνιδιών στο Flick σε 5 βήματα: 5 βήματα

Σχεδιασμός παιχνιδιών στο Flick σε 5 βήματα: Το Flick είναι ένας πραγματικά απλός τρόπος δημιουργίας ενός παιχνιδιού, ειδικά κάτι σαν παζλ, οπτικό μυθιστόρημα ή παιχνίδι περιπέτειας

Σύστημα ειδοποίησης αντίστροφης στάθμευσης αυτοκινήτου Arduino - Βήματα βήμα προς βήμα: 4 βήματα

Σύστημα ειδοποίησης αντίστροφης στάθμευσης αυτοκινήτου Arduino | Βήματα βήμα προς βήμα: Σε αυτό το έργο, θα σχεδιάσω ένα απλό κύκλωμα αισθητήρα στάθμευσης αντίστροφης στάθμευσης αυτοκινήτου Arduino χρησιμοποιώντας Arduino UNO και υπερηχητικό αισθητήρα HC-SR04. Αυτό το σύστημα ειδοποίησης αυτοκινήτου με βάση το Arduino μπορεί να χρησιμοποιηθεί για αυτόνομη πλοήγηση, κλίμακα ρομπότ και άλλα εύρη

Ανίχνευση προσώπου στο Raspberry Pi 4B σε 3 βήματα: 3 βήματα

Ανίχνευση προσώπου στο Raspberry Pi 4B σε 3 βήματα: Σε αυτό το Instructable πρόκειται να πραγματοποιήσουμε ανίχνευση προσώπου στο Raspberry Pi 4 με το Shunya O/S χρησιμοποιώντας τη βιβλιοθήκη Shunyaface. Το Shunyaface είναι μια βιβλιοθήκη αναγνώρισης/ανίχνευσης προσώπου. Το έργο στοχεύει στην επίτευξη της ταχύτερης ταχύτητας ανίχνευσης και αναγνώρισης με

Πώς να κάνετε Autotune (δωρεάν!): 4 βήματα

Πώς να κάνετε Autotune (Δωρεάν!): Χρησιμοποιώντας το garageband, μάθετε πώς να δημιουργείτε εύκολα αυτό το εφέ αυτόματης ακρόασης που ακούτε τόσο πολύ. ** ΕΠΕΞΕΡΓΑΣΙΑ ** Σύνδεση με ένα παράδειγμα: http://limelinx.com/files/e7b32e25dda5c5a22ab1bfc8c0eb3acd