Πίνακας περιεχομένων:

- Συγγραφέας John Day day@howwhatproduce.com.

- Public 2024-01-30 08:35.

- Τελευταία τροποποίηση 2025-01-23 14:39.

Σε αυτό το διδακτικό, θα σχεδιάσουμε ένα SPI Bus Master από την αρχή σε VHDL.

Βήμα 1: Επισκόπηση του SPI

- Το SPI είναι ένας σύγχρονος σειριακός δίαυλος

- Η δημοτικότητα και η απλότητά του το κατέστησαν ένα de facto πρότυπο στη σειριακή επικοινωνία

- Πλήρως διπλό λεωφορείο

- Απλό πρωτόκολλο και μεταξύ του ταχύτερου σειριακού διαύλου

Βήμα 2: Προδιαγραφές σχεδίασης

Αυτές είναι οι προδιαγραφές του SPI Master που σχεδιάζουμε:

- Υποστηρίζει και τους τέσσερις τρόπους λειτουργίας. δυναμικά διαμορφώσιμο

- Έλεγχος ενεργοποίησης ρολογιού για εξοικονόμηση ενέργειας

- Στατιστικά διαμορφώσιμο μήκος και ταχύτητα λέξης

- Ενιαία διακοπή τόσο για μετάδοση όσο και για λήψη

Βήμα 3: Εκκίνηση

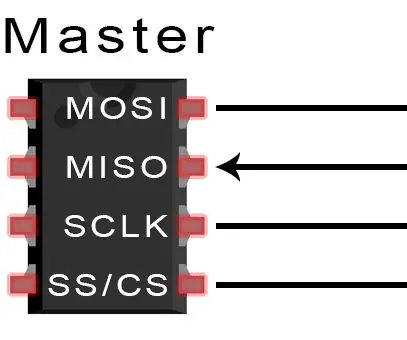

Πρώτα απ 'όλα, η IP μας πρέπει να έχει δύο διεπαφές. Το ένα είναι σειριακή διασύνδεση και το άλλο παράλληλη διεπαφή. Η σειριακή διεπαφή αποτελείται από τα de-facto τυπικά σήματα του SPI: MOSI, MISO, SS, SCLK.

Το MOSI μερικές φορές ονομάζεται SDO και το MISO μερικές φορές ονομάζεται SDI.

Η σειριακή διεπαφή χρησιμοποιείται για την επικοινωνία με εξωτερικά περιφερειακά, δηλαδή, υποτελείς SPI.

Η παράλληλη διασύνδεση χρησιμοποιείται για την επικοινωνία με τον κεντρικό υπολογιστή μας, δηλαδή, έναν μικροελεγκτή ή έναν μικροεπεξεργαστή, ο οποίος στην πραγματικότητα λέει στον Κύριο τα δεδομένα που πρέπει να μεταδοθούν και να ληφθούν σειριακά μέσω των σειριακών γραμμών. δηλαδή, όλοι οι δίαυλοι δεδομένων ανήκουν σε παράλληλη διεπαφή.

Έχουμε ένα παγκόσμιο ρολόι που οδηγεί την εσωτερική λογική SPI, καθώς και το SCLK, το οποίο παράγουμε εσωτερικά.

Έχουμε επίσης κάποια σήματα ελέγχου όπως εγγραφή ενεργοποίησης, ενεργοποίηση ρολογιού. Διακοπή και άλλα σήματα κατάστασης.

Δεδομένου ότι πρέπει να αντιμετωπίσουμε σύνθετες συνθήκες ελέγχου, είναι πιο απλό να σχεδιάσουμε τέτοιες σειριακές IP επικοινωνίας ως FSM. Θα σχεδιάσουμε το SPI master και ως FSM. Το FSM θα οδηγείται από ένα άλλο εσωτερικό ρολόι που είναι δύο φορές SCLK. Αυτό το εσωτερικό ρολόι δημιουργείται χρησιμοποιώντας σύγχρονους μετρητές από το παγκόσμιο ρολόι.

Όλα τα σήματα ελέγχου που διασταυρώνουν τομείς ρολογιού διαθέτουν συγχρονιστές στην ασφαλέστερη πλευρά.

Βήμα 4: Προβολή RTL των κυματομορφών SPI Master Core και Simulation

Είναι ένας γυμνός σχεδιασμός RTL χωρίς αποκλειστικές IP FPGA που χρησιμοποιούνται. Ως εκ τούτου, είναι ένας πλήρως φορητός κώδικας σε οποιοδήποτε FPGA.

Συνιστάται:

Η μέτρηση του καρδιακού ρυθμού σας βρίσκεται στην άκρη του δακτύλου σας: Προσέγγιση φωτοπληθυσμογραφίας για τον προσδιορισμό του καρδιακού ρυθμού: 7 βήματα

Η μέτρηση του καρδιακού ρυθμού σας βρίσκεται στην άκρη του δακτύλου σας: Προσέγγιση φωτοπληθυσμογραφίας για τον προσδιορισμό του καρδιακού ρυθμού: Ο φωτοπληθυσμογράφος (PPG) είναι μια απλή και χαμηλού κόστους οπτική τεχνική που χρησιμοποιείται συχνά για τον εντοπισμό αλλαγών στον όγκο αίματος σε μια μικροαγγειακή κλίνη ιστού. Χρησιμοποιείται κυρίως μη επεμβατικά για την πραγματοποίηση μετρήσεων στην επιφάνεια του δέρματος, συνήθως

Σχεδιασμός I2C Master σε VHDL: 5 βήματα

Σχεδιασμός του I2C Master σε VHDL: Σε αυτό το διδακτικό, συζητείται ο σχεδιασμός ενός απλού I2C master στο VHDL. ΣΗΜΕΙΩΣΗ: κάντε κλικ σε κάθε εικόνα για να δείτε την πλήρη εικόνα

Σχεδιασμός του UART σε VHDL: 5 βήματα

Σχεδιασμός του UART σε VHDL: Το UART σημαίνει Universal Asynchronous Receiver Transmitter. Είναι το πιο δημοφιλές και απλό πρωτόκολλο σειριακής επικοινωνίας. Σε αυτό το διδακτικό, θα μάθετε πώς να σχεδιάζετε μια μονάδα UART σε VHDL

ΒΑΣΙΚΑ ΤΟΥ ΠΡΩΤΟΚΟΛΛΟΥ ΕΠΙΚΟΙΝΩΝΙΑΣ ΤΟΥ SPI: 13 Βήματα

ΒΑΣΙΚΑ ΤΟΥ ΠΡΩΤΟΚΟΛΛΟΥ ΕΠΙΚΟΙΝΩΝΙΑΣ SPI: Όταν συνδέετε έναν μικροελεγκτή σε έναν αισθητήρα, οθόνη ή άλλη μονάδα, σκέφτεστε ποτέ πώς οι δύο συσκευές μιλούν μεταξύ τους; Τι ακριβώς λένε; Πώς είναι σε θέση να καταλάβουν ο ένας τον άλλον; Επικοινωνία μεταξύ ηλεκτρονικού devic

Χρήση του PSP ως Joystick του υπολογιστή και στη συνέχεια έλεγχος του υπολογιστή σας με το PSP: 5 βήματα (με εικόνες)

Χρήση του PSP ως Joystick του υπολογιστή και στη συνέχεια έλεγχος του υπολογιστή σας με το PSP: Μπορείτε να κάνετε πολλά ωραία πράγματα με το PSP homebrew και σε αυτό το εκπαιδευτικό πρόγραμμα θα σας μάθω πώς να χρησιμοποιείτε το PSP σας ως χειριστήριο για παιχνίδια, αλλά υπάρχει επίσης ένα πρόγραμμα που σας επιτρέπει να χρησιμοποιείτε το joystick ως ποντίκι. Εδώ είναι η μητέρα