Πίνακας περιεχομένων:

- Βήμα 1: Διάγραμμα αποκλεισμού

- Βήμα 2: Αρχή λειτουργίας

- Βήμα 3: Εφαρμογή λογικής

- Βήμα 4: Επίλυση του αδιεξόδου

- Βήμα 5: Διαμόρφωση συσκευής - κύκλωμα Matrix0

- Βήμα 6: Διαμόρφωση συσκευής - Λογική ρολογιού SPI

- Βήμα 7: Διαμόρφωση συσκευής - Ιδιότητες συστατικών Matrix0

- Βήμα 8: Διαμόρφωση συσκευής - κύκλωμα Matrix1

- Βήμα 9: Διαμόρφωση συσκευής - Δυαδικός μετρητής 3 -bit

- Βήμα 10: Διαμόρφωση συσκευής - Λογική σύγκρισης 3 -bit

- Βήμα 11: Διαμόρφωση συσκευής - Compηφιακή σύγκριση λογικής και προσωρινού μητρώου

- Βήμα 12: Διαμόρφωση συσκευής - Ιδιότητες συστατικών Matrix1

- Βήμα 13: Αποτελέσματα

- Συγγραφέας John Day day@howwhatproduce.com.

- Public 2024-01-30 08:33.

- Τελευταία τροποποίηση 2025-01-23 14:39.

Τα συστήματα ελέγχου και οι σχετικές συσκευές αντιμετωπίζουν πολλαπλές πηγές ενέργειας, όπως γραμμές πόλωσης ή μπαταρίες, και πρέπει να παρακολουθούν την υψηλότερη (ή τη χαμηλότερη) γραμμή μεταξύ ενός δεδομένου συνόλου.

Για παράδειγμα, η εναλλαγή φορτίου σε σύστημα με πολλαπλή μπαταρία απαιτεί το σύστημα να παρακολουθεί είτε την ελάχιστη είτε τη μέγιστη τάση μεταξύ της συστοιχίας μπαταριών (μέγιστη ή ελάχιστη ως συνάρτηση του συγκεκριμένου αλγορίθμου μεταγωγής) και να κατευθύνει δυναμικά το φορτίο στο καταλληλότερη πηγή σε πραγματικό χρόνο. Εναλλακτικά, το σύστημα μπορεί να χρειαστεί να αποσυνδέσει προσωρινά τη μπαταρία χαμηλότερης τάσης για σωστή φόρτιση.

Ένα άλλο παράδειγμα είναι το σύγχρονο σύστημα ηλιακής ενέργειας, όπου κάθε ηλιακός πίνακας είναι εξοπλισμένος με μηχανισμό κλίσης και με κύκλωμα ηλιακής παρακολούθησης (το τελευταίο παρέχει πληροφορίες θέσης του Sunλιου για τον προσανατολισμό του πίνακα). Με τις πληροφορίες μέγιστης τάσης, κάθε θέση ηλιακού πίνακα μπορεί να ρυθμιστεί με βάση το πάνελ της χορδής που παρέχει στην πραγματικότητα την υψηλότερη τάση εξόδου, επιτυγχάνοντας έτσι ένα ανώτερο επίπεδο βελτιστοποίησης ισχύος.

Υπάρχουν αρκετές διαφορετικές μάρκες εμπορικών IC (κυρίως μικροελεγκτές) που μπορούν κατ 'αρχήν να υλοποιήσουν ένα μέγιστο όριο τάσης. Ωστόσο, απαιτούν προγραμματισμό και είναι λιγότερο οικονομικά αποδοτικές από μια λύση μικτού σήματος. Η συμπλήρωση ενός σχεδίου Dialog GreenPAKTM μπορεί να επηρεάσει θετικά την προσιτή τιμή, το μέγεθος και την αρθρωτότητα του σχεδίου. Αυτός ο σχεδιασμός εκμεταλλεύεται το όφελος της ενσωμάτωσης τόσο του αναλογικού όσο και του ψηφιακού κυκλώματος σε ένα μόνο τσιπ.

Σε αυτό το Instructable, εφαρμόζεται το αναλογικό front-end και η ψηφιακή λογική που απαιτούνται για την υλοποίηση ενός ανιχνευτή μέγιστης (ή τελικά ελάχιστης) τάσης μεταξύ οκτώ διαφορετικών πηγών.

Για την εφαρμογή της αναλογικής οθόνης τάσης 8 καναλιών max/min, χρησιμοποιείται ένα SLG46620G.

Παρακάτω περιγράψαμε τα βήματα που απαιτούνται για να κατανοήσουμε πώς έχει προγραμματιστεί η λύση για τη δημιουργία της αναλογικής οθόνης τάσης 8 καναλιών max/min. Ωστόσο, εάν θέλετε απλώς να λάβετε το αποτέλεσμα προγραμματισμού, κατεβάστε το λογισμικό GreenPAK για να δείτε το ήδη ολοκληρωμένο GreenPAK Design File. Συνδέστε το GreenPAK Development Kit στον υπολογιστή σας και πατήστε το πρόγραμμα για να δημιουργήσετε την αναλογική οθόνη τάσης 8 καναλιών max/min.

Βήμα 1: Διάγραμμα αποκλεισμού

Το Σχήμα 1 δείχνει το γενικό διάγραμμα του υλοποιημένου συστήματος.

Μια συμβολοσειρά έως και 8 πηγών μεταβλητής τάσης πολυπλέκεται και διασυνδέεται με τη μονάδα ADC της GreenPAK που συνδέεται με μια προσαρμοσμένη εσωτερική σχεδίαση ικανή να επιλέξει την πηγή με την υψηλότερη τάση σε σχέση με τις άλλες. Η εσωτερική λογική εξάγει αυτές τις πληροφορίες για εμφάνιση ή περαιτέρω επεξεργασία.

Ο σχεδιασμός βασίζεται στο προϊόν GreenPAK SLG46620G, επειδή ενσωματώνει όλα τα απαραίτητα αναλογικά και ψηφιακά δομικά στοιχεία για την εφαρμογή. Σε αυτήν την εφαρμογή, ο πίνακας σαρώνεται μέσω ενός αναλογικού πολυπλέκτη ADG508 που κατευθύνεται απευθείας από το IC GreenPAK.

Οι πληροφορίες εξόδου είναι ένας ψηφιακός αριθμός 3-bit που αντιστοιχεί στον αριθμό πηγής τάσης στη μέγιστη τάση. Ένας άμεσος τρόπος για να λάβετε αυτές τις πληροφορίες είναι να δείξετε τον αριθμό μέσω μιας οθόνης 7 τμημάτων. Μπορεί να επιτευχθεί εύκολα διασυνδέοντας την ψηφιακή έξοδο του SLG46620G σε ένα πρόγραμμα οδήγησης οθόνης 7 τμημάτων, όπως η λύση GreenPAK που περιγράφεται στην Αναφορά ή σε ένα κοινό 74LS47 IC.

Το κύκλωμα που παρουσιάζεται αναζητά τη μέγιστη τάση. Για να μετατρέψετε το σχέδιο σε ανιχνευτή ελάχιστης τάσης, πρέπει να προστεθεί ένα απλό κύκλωμα προ-προετοιμασίας μεταξύ του αναλογικού πολυπλέκτη και της αναλογικής εισόδου GreenPAK, αφαιρώντας την έξοδο του πολυπλέκτη από μια τάση αναφοράς 1 V.

Βήμα 2: Αρχή λειτουργίας

Ο σχεδιασμός στοχεύει στην επιλογή της πηγής με μέγιστη τάση, επομένως πραγματοποιείται σάρωση σε ολόκληρη τη συστοιχία ενώ αποθηκεύεται η τιμή τελευταίας μέγιστης τιμής και συγκρίνεται με την επόμενη τιμή στην είσοδο (η οποία ανήκει στην επόμενη πηγή τάσης στη σάρωση).

Στη συνέχεια θα αναφερθούμε σε μια πλήρη ακολουθία πολυπλεξίας σε όλες τις εισόδους ως "σάρωση" ή "βρόχος".

Η σύγκριση μεταξύ δύο τιμών δεν επιτυγχάνεται μέσω εξαρτημάτων ACMP (ωστόσο, διατίθενται στο SLG46620G), αλλά μάλλον μέσω της μονάδας DCMP, όταν οι τιμές ψηφιοποιηθούν αντίστοιχα. Αυτή είναι μια προηγμένη και εκλεπτυσμένη τεχνική που αναφέρεται για πρώτη φορά στο Reference.

Το σχήμα 2 δείχνει πώς είναι δομημένο το SLG46620G για αυτό το σχέδιο.

Το αναλογικό σήμα εισόδου πηγαίνει στην είσοδο ADC μέσω του στοιχείου PGA με ένα σύνολο Gain 1. Διάφορες ρυθμίσεις Gain είναι επίσης δυνατό για να βρεθεί η καλύτερη αντιστοιχία με τα ηλεκτρονικά εξαρτήματα κλιματισμού που είναι αφιερωμένα στη χαρτογράφηση των τάσεων εισόδου στο 0-1 V σειρά της μονάδας GreenPAK ADC.

Το ADC λειτουργεί σε λειτουργία μονής λήξης και μετατρέπει το αναλογικό σήμα σε ψηφιακό κωδικό 8 bit, ο οποίος στη συνέχεια μεταφέρεται στη μονάδα DCMP. Ο ψηφιακός κώδικας εισάγεται επίσης στο μπλοκ SPI, που έχει ρυθμιστεί ως ρυθμιστικό ADC/FSM, όπου μπορεί να αποθηκευτεί και να μην αλλάξει ένας ψηφιακός κωδικός μέχρι να έρθει ο επόμενος παλμός στην είσοδο SPI CLK. Παρατηρήστε ότι ένα αποκλειστικό λογικό μπλοκ οδηγεί την είσοδο SPI CLK. Θα διερευνήσουμε αυτό το μέρος αργότερα, καθώς αυτή είναι η «βασική» λογική που είναι υπεύθυνη για τη σωστή λειτουργία. Ένας νέος ψηφιακός κωδικός αποθηκεύεται στη μονάδα SPI μόνο εάν ανήκει στην πραγματική μέγιστη τάση εισόδου.

Το στοιχείο DCMP χρησιμοποιείται για τη σύγκριση των τρεχόντων δεδομένων ADC με τον τελευταίο νικητή (δηλαδή το τελευταίο μέγιστο που βρέθηκε), το οποίο είναι αποθηκευμένο στο μπλοκ SPI. Θα παράγει έναν παλμό στην έξοδο OUT+ όταν τα νέα δεδομένα ADC είναι μεγαλύτερα από τα προηγούμενα. Χρησιμοποιούμε το σήμα OUT+ για να ενημερώσουμε το μπλοκ SPI με τον νέο νικητή.

Ένα παγκόσμιο σήμα ρολογιού οδηγεί τις μετατροπές ADC και τους γενικούς χρονισμούς. Μόλις πραγματοποιηθεί μια μετατροπή, το σήμα εξόδου INT του ADC χτυπά, συντονίζεται έγκαιρα με την παράλληλη έξοδο δεδομένων ADC. Χρησιμοποιούμε την έξοδο INT επίσης για να αυξήσουμε έναν δυαδικό μετρητή 3-bit, που εφαρμόζεται από DFF στο Matrix1, ο οποίος είναι χρήσιμος για τρεις λόγους:

1. Οι γραμμές εξόδου μετρητή απευθύνονται στον εξωτερικό αναλογικό πολυπλέκτη, εξυπηρετώντας έτσι την επόμενη τάση εισόδου στο ADC.

2. Η καταμέτρηση παγώνει σε έναν καταχωρητή 3-bit (εφαρμόζεται στο Matrix1) για να αποθηκεύσει τον προσωρινό νικητή κατά τη διάρκεια μιας σάρωσης.

3. Η καταμέτρηση αποκωδικοποιείται για την ενημέρωση ενός δεύτερου καταχωρητή 3-bit (που εφαρμόζεται στο Matrix0) μόλις ολοκληρωθεί η σάρωση.

Βήμα 3: Εφαρμογή λογικής

Η μονάδα ADC παρέχει διαδοχικά μετατρεπόμενα δεδομένα όλων των τάσεων εισόδου, η μία μετά την άλλη, επ 'αόριστον. Μόλις ο Multiplexer απευθυνθεί 0b111 (δεκαδικό 7), ο μετρητής κυλάει στο 0b000 (δεκαδικό 0) ξεκινώντας έτσι μια νέα σάρωση των τάσεων εισόδου.

Κατά τη διάρκεια της σάρωσης, δημιουργείται το σήμα εξόδου ADC INT όταν η παράλληλη έξοδος δεδομένων είναι έγκυρη. Όταν αυτό το σήμα πάλλεται, ο αναλογικός πολυπλέκτης πρέπει να μεταβεί στην επόμενη είσοδο, παρέχοντας στο PGA την αντίστοιχη τάση. Επομένως, η έξοδος ADC INT είναι το άμεσο σήμα χρονισμού του δυαδικού μετρητή 3-bit του σχήματος 2, του οποίου η παράλληλη λέξη εξόδου 3-bit απευθύνεται απευθείας στον εξωτερικό αναλογικό πολυπλέκτη ("V select" στο σχήμα 1).

Ας αναφερθούμε τώρα σε ένα παράδειγμα όπου οι τάσεις εισόδου υποτίθεται ότι έχουν τις ακόλουθες σχέσεις:

α) V0 <V1 <V2

β) V2> V3, V4

γ) V5> V2

Το σχήμα 3 αντιπροσωπεύει τα κύρια σήματα που εμπλέκονται στο μηχανισμό λήψης αποφάσεων max.

Δεδομένου ότι τα δεδομένα τελικά συγχρονίζονται στον καταχωρητή προσωρινής αποθήκευσης SPI συγχρόνως με παλμούς INT, υπάρχει ένα παράθυρο σύγκρισης όπου το περιεχόμενο του buffer SPI συγκρίνεται με το επόμενο αποτέλεσμα μετατροπής ADC. Αυτός ο συγκεκριμένος χρονισμός έχει ως αποτέλεσμα την παραγωγή παλμών OUT+ στην έξοδο DCMP. Μπορούμε να επωφεληθούμε από αυτούς τους παλμούς για να φορτώσουμε νέες τιμές στον καταχωρητή buffer SPI.

Όπως φαίνεται από τη γραμμή δεδομένων προσωρινής αποθήκευσης SPI του προηγούμενου σχήματος, ο καταχωρητής SPI περιέχει πάντα, κατά καιρούς, τη μεγαλύτερη τιμή μεταξύ των 8 εισόδων και ενημερώνεται μόνο όταν ανιχνεύεται μεγαλύτερη τιμή από τη μονάδα DCMP (αναφερόμενη στο DCMP OUT+ γραμμή εξόδου του γραφήματος, οι παλμοί που λείπουν κάνουν το V2 να παραμείνει κλειδωμένο στον καταχωρητή μέχρι να συγκριθεί με το V5).

Βήμα 4: Επίλυση του αδιεξόδου

Εάν η εφαρμοσμένη λογική θα ήταν ακριβώς όπως περιγράφηκε παραπάνω, είναι σαφές ότι θα βρεθούμε σε μια κατάσταση αδιεξόδου: το σύστημα είναι σε θέση να ανιχνεύσει μόνο τάσεις υψηλότερες από αυτήν που αντιστοιχεί σε αυτό που είναι αποθηκευμένο στον καταχωρητή προσωρινής αποθήκευσης SPI.

Αυτό ισχύει επίσης σε περίπτωση που αυτή η τάση μειωθεί και στη συνέχεια μια άλλη είσοδος, έως τώρα χαμηλότερη από αυτήν, γίνει η υψηλότερη: δεν θα ανιχνευθεί ποτέ. Αυτή η κατάσταση εξηγείται καλύτερα στο σχήμα 4 όπου υπάρχουν μόνο 3 τάσεις εισόδου για χάρη σαφήνεια.

Τη στιγμή της επανάληψης 2, το V3 πέφτει και το V1 είναι η πραγματική μέγιστη τάση. Αλλά η μονάδα DCMP δεν παρέχει παλμό επειδή τα δεδομένα που αποθηκεύονται στον καταχωρητή buffer SPI (που αντιστοιχεί σε 0.6 V) είναι μεγαλύτερα από αυτά που αντιστοιχούν στο V1 (0.4 V).

Στη συνέχεια, το σύστημα συμπεριφέρεται ως ένα "απόλυτο" εργαλείο εύρεσης max και δεν ενημερώνει σωστά την έξοδο.

Ένας καλός τρόπος για να ξεπεραστεί αυτό το πρόβλημα είναι να αναγκαστεί η επαναφόρτωση των δεδομένων στο SPI Buffer Register όταν το σύστημα ολοκληρώσει έναν πλήρη κύκλο ψηφοφορίας όλων των καναλιών.

Στην πραγματικότητα, εάν η τάση σε αυτήν την είσοδο εξακολουθεί να είναι η υψηλότερη, τίποτα δεν αλλάζει και ο έλεγχος συνεχίζεται με ασφάλεια (αναφερόμενοι στο Σχήμα 4 παραπάνω, αυτή είναι η περίπτωση των Επαναλήψεων Βρόχου 0 και 1). Από την άλλη πλευρά, εάν η τάση σε αυτήν την είσοδο κατά τύχη μειωθεί σε μια τιμή μικρότερη από μια άλλη είσοδο, τότε η επαναφόρτωση της τιμής δίνει τη δυνατότητα στη μονάδα DCMP να παράγει έναν παλμό OUT+ όταν τη συγκρίνει με τη νέα μέγιστη τιμή (αυτή είναι η περίπτωση επαναλήψεων βρόχου 2 και 3).

Ένα κομμάτι λογικού κυκλώματος είναι απαραίτητο για να ξεπεραστεί το πρόβλημα. Πρέπει να παράγει ένα σήμα ρολογιού στο στοιχείο SPI όταν ο βρόχος φτάσει στην πραγματική μέγιστη είσοδο, αναγκάζοντας έτσι μια επαναφόρτωση της ενημερωμένης λέξης δεδομένων του στο SPI Buffer Register. Αυτό θα συζητηθεί στις ενότητες 7.2 και 7.6 παρακάτω.

Βήμα 5: Διαμόρφωση συσκευής - κύκλωμα Matrix0

Το SLG46620G έχει δύο μπλοκ μήτρας, όπως απεικονίζεται στο σχήμα 2. Τα παρακάτω σχήματα δείχνουν τις αντίστοιχες διαμορφώσεις συσκευής.

Το πάνω μέρος του κυκλώματος είναι το "Loop Register" που πραγματοποιείται με 3 DFF (DFF0, DFF1 και DFF2). Ανανεώνεται μετά από κάθε βρόχο του πολυπλέκτη εισόδου για να στείλετε σε ένα πρόγραμμα οδήγησης οθόνης 7 τμημάτων τον δυαδικό αριθμό του "νικητή", δηλαδή την είσοδο με την υψηλότερη τάση στην τελευταία σάρωση. Τόσο το ρολόι προς τα DFF όσο και τα δεδομένα προέρχονται από τη λογική που εφαρμόζεται στο Matrix1 μέσω, αντίστοιχα, των θυρών P12, P13, P14 και P15.

Το κάτω μέρος είναι το αναλογικό μπροστινό άκρο με είσοδο στο Pin 8 και PGA με κέρδος x1. Η έξοδος ADC INT πηγαίνει τόσο στη λογική χρονισμού του SPI όσο και στο Matrix1 μέσω της θύρας P0, όπου θα χρησιμεύσει ως σήμα ρολογιού για τον μετρητή που εφαρμόζεται.

Οι παράλληλες έξοδοι δεδομένων ADC και SPI φέρουν αντίστοιχη ένδειξη NET11 και NET15 για σύνδεση στο εξάρτημα DCMP στο Matrix1.

Βήμα 6: Διαμόρφωση συσκευής - Λογική ρολογιού SPI

Όπως επισημάνθηκε προηγουμένως στην ενότητα "Logic Implementation", το SPI Buffer Register ενημερώνεται κάθε φορά που μια σύγκριση μεταξύ της πραγματικής αποθηκευμένης τιμής και των νέων δεδομένων μετατροπής ADC δημιουργεί παλμό στην έξοδο DCMP OUT+.

Η ακεραιότητα του σήματος διασφαλίζεται εάν αυτό το σήμα είναι AND-ed με την έξοδο ADC INT. Αυτό αποφεύγει κάθε ακίδα και ψευδή ενεργοποίηση.

Υπογραμμίσαμε επίσης ότι για να παραλείψετε αδιέξοδες καταστάσεις, το SPI Buffer πρέπει να ενημερωθεί όταν ο βρόχος φτάσει στα πραγματικά δεδομένα νικητή.

Τρία σήματα βρίσκονται στο παιχνίδι για σωστή χρονομέτρηση SPI:

1. Έξοδος ADC INT (LUT0-IN1)

2. DCMP OUT+ έξοδος (LUT0-IN0 μέσω θύρας P10)

3. Η μέτρηση ισούται με σήμα ασφάλισης (LUT0-IN2 μέσω θύρας P11)

Τα δύο πρώτα είναι AND-ed και τα δύο OR-ed με το τελευταίο στο LUT0, των οποίων η εφαρμογή έχει διαμορφωθεί όπως στο Σχήμα 6.

Βήμα 7: Διαμόρφωση συσκευής - Ιδιότητες συστατικών Matrix0

Τα Σχήματα 7-10 δείχνουν τα υπόλοιπα παράθυρα ιδιοτήτων συστατικών που ανήκουν στο Matrix0.

Βήμα 8: Διαμόρφωση συσκευής - κύκλωμα Matrix1

Βήμα 9: Διαμόρφωση συσκευής - Δυαδικός μετρητής 3 -bit

Το επάνω μέρος του κυκλώματος περιέχει λογικά στοιχεία, κυρίως έναν δυαδικό μετρητή 3-bit χρονομετρημένο από την έξοδο ADC INT, όπως ήδη συζητήθηκε. Αυτός ο μετρητής υλοποιείται με ένα αρκετά "τυπικό" σχηματικό σχήμα που φαίνεται στο σχήμα 12.

Αυτός ο μετρητής υλοποιείται στο σχεδιασμό μας μέσω των Flip-Flops DFF9, DFF10, DFF11 και INV1, LUT4, LUT8. Η έξοδος DFF9 είναι η LSB ενώ η DFF11 είναι η MSB όπως φαίνεται στο σχήμα 13.

Το LUT4 έχει διαμορφωθεί ως XOR ενώ το LUT8 εκτελεί τη λογική AND-XOR της Εικόνας 12.

Οι έξοδοι μετρητή πηγαίνουν σε τρεις ψηφιακές ακίδες εξόδου για να αντιμετωπίσουν τον εξωτερικό αναλογικό πολυπλέκτη.

Το LUT10 αποκωδικοποιεί τον κωδικό του μετρητή όταν ολοκληρωθεί η σάρωση και τροφοδοτεί έναν παλμό στο Matrix0 μέσω του DLY8 και της θύρας P12. Αυτό απλώς επιτυγχάνεται με AND-ing τις εξόδους του μετρητή, αποκωδικοποιώντας έτσι τον αριθμό 7 dec (0b111 δυαδικό, τέλος βρόχου).

Βήμα 10: Διαμόρφωση συσκευής - Λογική σύγκρισης 3 -bit

Το σχήμα 15 δείχνει το κύκλωμα που χρησιμοποιείται για την ανίχνευση πότε ο βρόχος επαναλαμβάνεται στην τρέχουσα διεύθυνση "νικητή". Σε αυτήν την περίπτωση, όπως ήδη συζητήθηκε, ένας ψηφιακός παλμός θα πρέπει να αναγκάσει μια επαναφόρτωση του τρέχοντος αποτελέσματος ADC για να λύσει μια πιθανή κατάσταση αδιεξόδου.

Η διεύθυνση "νικητής" αποθηκεύεται στον προσωρινό μητρώο του Matrix1 (δείτε παρακάτω), ενώ η τρέχουσα διεύθυνση εξάγεται από τον δυαδικό μετρητή.

Οι πύλες XNOR παρέχουν μια πραγματική (λογική 1 ή «υψηλή») έξοδο όταν και οι δύο είσοδοι είναι ίσες. AND-ing αυτό το σήμα για όλα τα bits (LUT9) μας δίνει έναν παλμό όταν και οι δύο δυαδικοί κώδικες είναι οι ίδιοι. Λεπτομέρειες σχετικά με τις πύλες XOR ως έλεγχος ισοτιμίας μπορείτε να βρείτε στο Reference.

Το σήμα «Counter-equals-Latch» διαβιβάζεται στο Matrix0 μέσω της θύρας P11.

Βήμα 11: Διαμόρφωση συσκευής - Compηφιακή σύγκριση λογικής και προσωρινού μητρώου

Το κάτω μέρος του σχήματος 11 (επισημαίνεται στο σχήμα 16) δείχνει το μπλοκ DCMP, το τμήμα λήψης αποφάσεων αυτού του σχεδίου.

Το DFF6, 7 και 8 σχηματίζουν έναν καταχωρητή 3-bit για την αποθήκευση του προσωρινού αριθμού εισόδου "νικητής" ενώ ο βρόχος εκτελείται. Οι είσοδοι στα Flip-Flops είναι οι δυαδικές έξοδοι μετρητή 3-bit, όπως είναι ορατές στο παγκόσμιο κύκλωμα Matrix1 της Εικόνας 11, που παραλείπεται εδώ για λόγους σαφήνειας.

Οι έξοδοι αυτού του καταχωρητή δεν μπορούν να οδηγήσουν απευθείας την οθόνη 7 τμημάτων, επειδή η τιμή που αποθηκεύεται εδώ αλλάζει κατά τη διάρκεια μιας σάρωσης και θα πρέπει να θεωρείται «έγκυρη» μόνο στο τέλος της ίδιας της σάρωσης.

Για το λόγο αυτό, οι έξοδοι προσωρινών καταχωρητών συνδέονται με το Matrix0's Loop Register μέσω των θύρων inter-matrix P13, P14 και P15.

Είναι σημαντικό να παρατηρήσετε στο Σχήμα 16 ότι ο προσωρινός καταχωρητής χρονομετρείται με την έξοδο DCMP OUT+ όταν το ADC-SPI καταχωρεί αποτελέσματα σύγκρισης σε ένα νέο μέγιστο που βρέθηκε.

Το ίδιο σήμα OUT+ διαβιβάζεται στο Matrix0, SPI CLK Logic, μέσω της θύρας P10.

Βήμα 12: Διαμόρφωση συσκευής - Ιδιότητες συστατικών Matrix1

Τα Σχήματα 17-19 δείχνουν τα παράθυρα ιδιοτήτων συστατικών που ανήκουν στο Matrix1.

Βήμα 13: Αποτελέσματα

Για τον έλεγχο της εφαρμογής, έχει κατασκευαστεί ένα πρωτότυπο πίνακα αξιολόγησης, όπου οι 8 αναλογικές τάσεις εισόδου λαμβάνονται από μια σειρά διαχωριστικών αντιστάσεων με TrimPots (όπως φαίνεται στο σχήμα 20).

Ο πολυπλέκτης που χρησιμοποιείται είναι ένα ADG508, ένα μέρος που μπορεί να λειτουργήσει με μία μόνο παροχή (12 V).

Το πρόγραμμα οδήγησης οθόνης 7 τμημάτων είναι 74LS47. Αποκωδικοποιεί μια παράλληλη λέξη εισόδου και οδηγεί απευθείας μια κοινή άνοδο 7 τμημάτων οθόνης.

Ο πίνακας αξιολόγησης διαθέτει σύνδεσμο ορθής γωνίας 2x10 για σύνδεση απευθείας σε μια πλατφόρμα προηγμένης ανάπτυξης GreenPAK στον σύνδεσμο επέκτασής του, όπως φαίνεται στο σχήμα 21.

Η σύνδεση με την Πλατφόρμα Προχωρημένης Ανάπτυξης GreenPAK καθιστά πολύ απλή τη λήψη μετρήσεων των σημάτων για γρήγορο έλεγχο. Για παράδειγμα, το σχήμα 22 δείχνει ένα σύνολο σημάτων (αντίστοιχα CLOCK, έξοδο ADC INT και έξοδο DCMP OUT+) όπως καταγράφονται από έναν λογικό αναλυτή HP 54620A. Οι κυματομορφές ενεργοποιούνται από μια ανερχόμενη ακμή του σήματος OUT+ (στο πεδίο με την ένδειξη "A> B"), επομένως πρόκειται για σύλληψη κυματομορφής όταν ανιχνεύεται μια νέα μέγιστη τάση μεταξύ των αναλογικών εισόδων. Στην πραγματικότητα, αποκτήθηκε περιστρέφοντας ένα από τα TrimPots του πίνακα αξιολόγησης για να αυξηθεί η αντίστοιχη τάση που φαίνεται στο σχήμα 22.

Το σχήμα 23 δείχνει το σχηματικό σχήμα του πίνακα αξιολόγησης.

συμπέρασμα

Σε αυτό το Instructable, εφαρμόσαμε έναν ανιχνευτή μέγιστης (ή ελάχιστης) τάσης οκτώ καναλιών που θα χρησιμοποιηθεί ως κοινή προσθήκη σε συστήματα ελέγχου πολλαπλών καναλιών. Η προσέγγιση που παρουσιάζεται αξιοποιεί προηγμένα χαρακτηριστικά των συστατικών του GreenPAK και δείχνει πώς είναι δυνατή η ενσωμάτωση σε μία ενιαία αναλογική και ψηφιακή λειτουργία. Πολλά εμπορικά IC μπορούν να αντικατασταθούν με Dialog GreenPAK, έτσι ώστε να μειωθεί το μέγεθος και το κόστος της εφαρμογής.

Συνιστάται:

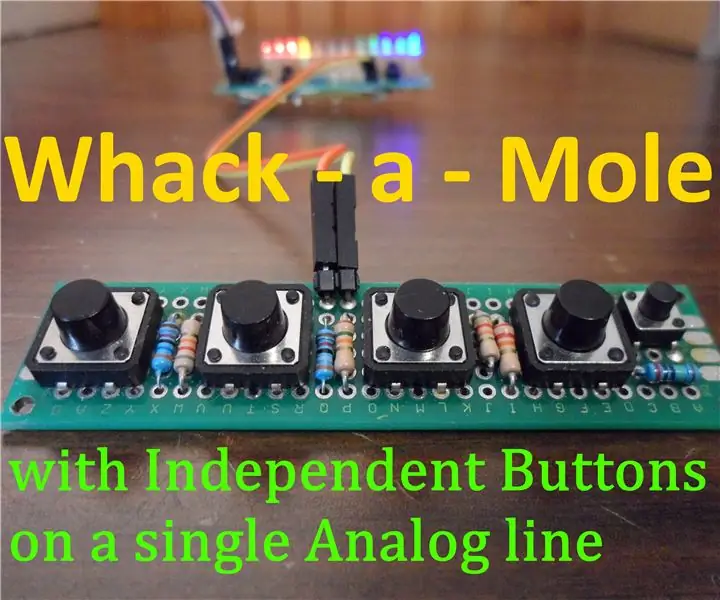

4 παιχνίδια με κουμπιά χρησιμοποιώντας μία αναλογική είσοδο: 6 βήματα (με εικόνες)

4 Παιχνίδια με κουμπιά χρησιμοποιώντας μία αναλογική είσοδο: Αυτό το εκπαιδευτικό πρόγραμμα εστιάζει στη χρήση μιας αναλογικής γραμμής εισόδου για πολλά κουμπιά που μπορούν να εντοπιστούν ανεξάρτητα το ένα από το άλλο. Και για να επισημάνετε τη χρήση αυτών των κουμπιών που περιλαμβάνονται είναι λογισμικό για την αναπαραγωγή τεσσάρων διαφορετικών παιχνιδιών 4 κουμπιών. Όλα τα παιχνίδια (8 σε

Ελάχιστη ρετρό κονσόλα παιχνιδιού ATBOY: 5 βήματα

ATBOY Minimal Retro Gaming Console: Μια μικρή ρετρό κονσόλα που μοιάζει με κονσόλα βασισμένη στο ATtiny85 x 0,96 OLED για παιχνίδι εισβολέων χώρου, Tetris κ.λπ

ΔΙΑΒΑΣΤΕ ΑΝΑΛΟΓΙΚΗ ΤΑΣΗ - ARDUINO - ΚΩΔΙΚΟΣ ΑΠΟΚΑΤΑΣΤΑΣΗ #1: 5 Βήματα

ΤΟΜΟΣ ΑΝΑΛΟΓΗΣ ΑΝΑΛΟΓΟΥ - ARDUINO - ΚΩΔΙΚΟΣ ΑΠΟΚΑΤΑΣΤΑΣΗ #1: ΚΩΔΙΚΟΣ ΑΠΟΚΑΤΑΣΤΑΣΗ #1READ ANALOG VOLTAGE: Αυτό το παράδειγμα σας δείχνει πώς να διαβάζετε μια αναλογική είσοδο στον αναλογικό pin 0, να μετατρέπετε τις τιμές από το analogRead () σε τάση και να το εκτυπώνετε στο σειριακό οθόνη του λογισμικού Arduino (IDE)

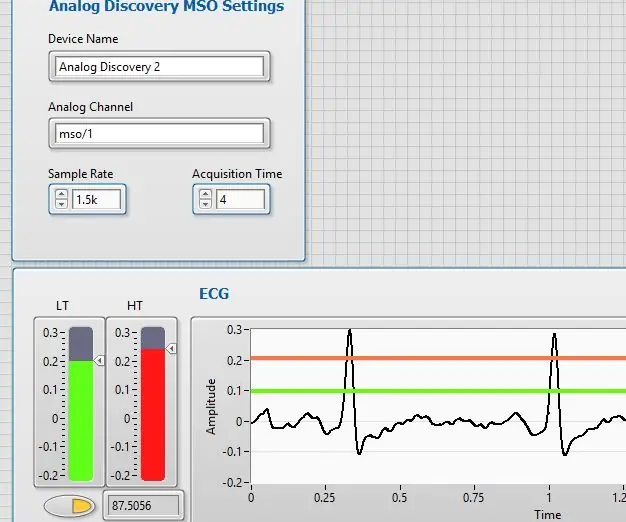

ΗΚΓ DIY χρησιμοποιώντας αναλογική ανακάλυψη 2 και LabVIEW: 8 βήματα

DIY ECG Χρησιμοποιώντας μια Αναλογική Ανακάλυψη 2 και LabVIEW: Σε αυτό το Instructable, θα σας δείξω πώς να φτιάξετε ένα σπιτικό ηλεκτροκαρδιογράφο (ΗΚΓ). Ο στόχος αυτού του μηχανήματος είναι να ενισχύσει, να μετρήσει και να καταγράψει το φυσικό ηλεκτρικό δυναμικό που δημιουργείται από την καρδιά. Ένα ΗΚΓ μπορεί να αποκαλύψει πληθώρα πληροφοριών για

Πώς να κάνετε τον φορητό υπολογιστή σας να εξοικονομεί ισχύ μπαταρίας με ελάχιστη απώλεια απόδοσης: 4 βήματα

Πώς να κάνετε τον φορητό υπολογιστή σας να εξοικονομεί ισχύ μπαταρίας με ελάχιστη απώλεια απόδοσης: Ποιος λέει ότι ο φορητός υπολογιστής σας πρέπει να υποφέρει αργά για να εξοικονομήσει λίγη ενέργεια; Το πόσο αλλάζει η απόδοση ή η διάρκεια ζωής της μπαταρίας σας εξαρτάται από την ηλικία του φορητού υπολογιστή σας, την ηλικία της μπαταρίας και άλλα προγράμματα και ρυθμίσεις. Ακολουθούν μερικά απλά βήματα που θα σας βοηθήσουν να αυξήσετε